### Technical University of Denmark

# Methods and Tools for the Analysis, Verification and Synthesis of Genetic Logic Circuits,

Baig, Hasan; Madsen, Jan; Pop, Paul

Publication date: 2017

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

*Citation (APA):* Baig, H., Madsen, J., & Pop, P. (2017). Methods and Tools for the Analysis, Verification and Synthesis of Genetic Logic Circuits, (DTU Compute PHD-2017, Vol. 456).

### DTU Library

Technical Information Center of Denmark

### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

### Methods and Tools for the Analysis, Verification and Synthesis of Genetic Logic Circuits

Hasan Baig

Kongens Lyngby 2017 PhD-2017-456

Technical University of Denmark Department of Applied Mathematics and Computer Science Richard Petersens Plads, building 324, 2800 Kongens Lyngby, Denmark Phone +45 4525 3031 compute@compute.dtu.dk www.compute.dtu.dk PhD-2017-456

# Summary (English)

Synthetic biology has emerged as an important discipline in which engineers and biologists are working together to design new and useful biological systems composed of genetic circuits. The purpose of developing genetic circuits is to carry out desired logical functions inside a living cell. This usually requires simulating the mathematical models of these genetic circuits and perceive whether or not the circuit behaves appropriately. Furthermore, synthetic biology utilizes the concepts from electronic design automation (EDA) of abstraction and automated construction to generate genetic circuits with the aim to reduce the in-vitro (wet-lab) experiments. To address this, several automated tools have been developed to improve the process of genetic design automation (GDA) with different capabilities. This thesis attempts to contribute to the advancement of GDA tools by introducing capabilities which we believe that no other existing GDA tools support.

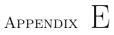

First, we introduce a user-friendly simulation tool, called D-VASim, which allows a user to perform virtual laboratory experimentation by dynamically interacting with the model during runtime. This dynamic interaction with the model gives user a feeling of being in the lab performing wet-lab experiments virtually. This tool allows users to perform both deterministic and stochastic simulations.

Next, this dissertation introduces a methodology to perform timing analyses of genetic logic circuits, which allows a user to analyze the threshold value and propagation delays of genetic logic circuits. In this thesis, it has been demonstrated, through *in-silico* experimentation, that the threshold value and propagation delay plays a vital role in the correct functioning of a genetic circuit. It has also been shown how some circuit parameters effect these two important design characteristics.

This thesis also introduces an automated approach to analyze the behavior of genetic logic circuits from the simulation data. With this capability, the boolean logic of complex genetic circuits can be analyzed and/or verified automatically. It is also shown in this thesis that the proposed approach is effective to determine the variation in the behavior of genetic circuits when the circuit's parameters are changed.

In addition, the thesis also attempts to propose a synthesis and technology mapping tool, called GeneTech, for genetic circuits. It allows users to construct a genetic circuit by only specifying its behavior in the form of a boolean expression. For technology mapping, this tool uses gate library developed by the collective efforts of the researchers at MIT and Boston universities. It is shown experimentally that the tool is able to provide all feasible solutions, containing different genetic components, to achieve the specified boolean behavior.

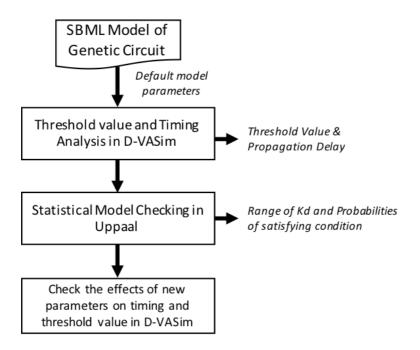

Finally, it has been shown how D-VASim can be used along with other tools for useful purposes, like model checking. With respect to this, an experimental workflow is proposed for checking genetic circuits using the statistical model checking (SMC) utility of the Uppaal tool and the timing analysis capability of D-VASim. We further demonstrated how the reliability of a simulation can be improved by using real parameter values. In this regard, the relationship between the simulation parameters and real parameters have been derived.

# Summary (Danish)

Syntetisk biologi er en ny og vigtig disciplin i hvilken ingeniører og biologer arbejder sammen om at designe nye og nyttige biologiske systemer, bestående af genetiske kredsløb. Formålet med udvikling af genetiske kredsløb er at udføre ønskede logiske funktioner i en levende celle. For at teste om det genetiske kredsløb opfører sig korrekt, udføres der normalt simuleringer af en model af det genetiske kredsløb. Syntetisk biologi udnytter begreber fra elektronisk designautomatisering (EDA), så som abstraktion og automatiseret konstruktion, til at genere genetiske kredsløb med det formål at reducere antallet af in-vitro forsøg (vådrums laboratorie eksperimenter), der ellers kræves for at finde en korrekt løsning. Forskere har i de senere år udviklet en række forskellige genetiske designautomatiserings (GDA) værktøjer til at forbedre denne proces. Denne afhandling bidrager til udviklingen af GDA værktøjer ved at introducere egenskaber, som vi mener at ingen eksisterende GDA-værktøj understøtter.

Først introducerer vi et brugervenligt simuleringsværktøj, kaldet D-VASim, som tillader brugeren at udføre virtuelle laboratorieforsøg gennem dynamisk interaktion med modellen under simuleringen. Denne dynamiske interaktion med modellen giver brugeren en følelse af at være i laboratoriet. D-VASim giver brugerne mulighed for at udføre både deterministiske og stokastiske simuleringer. Oven på simuleringsmodellen er der udviklet en metode til at udføre tidsanalyser af genetiske logiske kredsløb. Denne giver brugeren mulighed for at analysere logiske tærskelværdier og kredsløbsforsinkelser af genetiske logiske kredsløb. I denne afhandling er det, gennem in-silico eksperimenter, blevet påvist at tærskelværdien og kredsløbsforsinkelsen spiller en afgørende rolle for den korrekte funktion af et genetisk kredsløb, samt visse genetiske kredsløbsparametre påvirker disse to vigtige designegenskaber. Denne afhandling introducerer også en automatiseret analyse af opførslen af genetiske logiske kredsløb ud fra simuleringsdata. Herved kan boolesk logik af komplekse genetiske kredsløb analyseres og / eller verificeres automatisk. Det fremgår også af denne afhandling, at analysen er effektiv til at bestemme variationerne i opførsel af et givet genetiske kredsløb, når kredsløbets parametre ændres.

Endelig introducerer afhandlingen et syntese- og teknologi-mapings værktøj for genetiske kredsløb, kaldet GeneTech. Dette værktøj giver brugeren mulighed for at konstruere et genetisk kredsløb ved blot at specificere dets ønskede opførsel i form af booleske udtryk. Til teknologi-maping, bruges et genetisk komponent bibliotek udviklet af forskere ved MIT og Boston universitetet. Det vises eksperimentelt at GeneTech er i stand til at finde samtlige mulige løsninger, der potentielt kan realisere den specificerede booleske opførsel. Endelig er det vist, hvordan D-VASim kan bruges sammen med andre værktøjer, som f.eks. model checking. Der foreslås et eksperimentelt workflow til validering af genetiske kredsløb ved hjælp af det statistiske model checking (SMC) -værktøjet i Uppaal værktøjet og tidsanalyse delen af D-VASim. Yderligere demonstrerer vi, hvordan pålideligheden af en simulering kan forbedres ved bruge de reelle parameterværdier. I denne henseende er forholdet mellem simuleringsparametre og reelle parametre er blevet afledt.

## Preface

This thesis was prepared at the department of Applied Mathematics and Computer Science at the Technical University of Denmark (DTU) in fulfillment of the requirements for acquiring the degree of Doctor of Philosophy (PhD).

The thesis deals with the methods and tools for the simulation, analysis and synthesis of genetic logic circuits.

The research work presented in this thesis has been supervised by Professor Jan Madsen and co-supervised by Professor Paul Pop.

Lyngby, 14-August-2017

Hasan Baig

## **Research Dissemination**

The research work presented in this thesis has been disseminated in the following:

### Journals

- Hasan Baig and Jan Madsen, "Simulation Approach for Timing Analysis of Genetic Logic Circuits", ACS Synthetic Biology, 2017, 6 (7), pp 1169–1179. Published.

- Hasan Baig and Jan Madsen, "D-VASim An Interactive Virtual Laboratory Environment for the Simulation and Analysis of Genetic Circuits", *Bioinformatics*, vol. 33, issue 2, pp. 297–299, 2016. *Published*.

- Hasan Baig and Jan Madsen, "An Automated Approach to Verify the Logic of Genetic Circuits from Experimental data", ACM Journal on Emerging Technologies. Under review.

- Hasan Baig and Jan Madsen, "GeneTech: "A Technology Mapping Tool for Genetic Logic Circuits", IEEE Transactions on Biomedical Engineering. Under review.

#### Conferences

- Hasan Baig and Jan Madsen, "Taming Living Logic using Formal Methods", *Models, Algorithms, Logics and Tools*, LNCS Springer, 10460, pp. 503–515, 2017. *Published.*

- Hasan Baig and Jan Madsen, "Logic Analysis and Verification of n-input Genetic Logic Circuits", *Design Automation and Test in Europe (DATE)*, pp. 654–657, 2017. *Published*.

### Workshops

- Hasan Baig and Jan Madsen, "A Top-down Approach to Genetic Circuit Synthesis and Optimized Technology Mapping", 9th International Workshop on Bio-Design Automation (IWBDA), pp. 28–29, 2017. Published.

- Hasan Baig and Jan Madsen, "Logic and Timing Analysis of Genetic Logic Circuits using D-VASim", 8th International Workshop on Bio Design Automation (IWBDA), pp. 77–78, 2016. Published.

- Hasan Baig and Jan Madsen, "D-VASim: Dynamic Virtual Analyzer and Simulator for Genetic Circuits", 7th International Workshop on Bio-Design Automation (IWBDA), pp. 48–49, 2015. Published.

### Posters and Practical Demonstrations

- Hasan Baig and Jan Madsen, "Timing Analysis of Genetic Logic Circuits using D-VASim", At the University Booth in the Design Automation and Test in Europe (DATE), 2016. Presented and Published.

- Hasan Baig and Jan Madsen, "Analysis and Verification of Genetic Logic Circuits using D-VASim", At the 2nd Synthetic and Systems Biology Summer School (SSBSS), 2015. Presented.

### Industrial Case Studies

• Hasan Baig and Jan Madsen, "D-VASim: A Software Tool to Simulate and Analyze Genetic Logic Circuits", published by National Instruments (http:\www.ni.com) and can be seen at http://sine.ni.com/cs/app/ doc/p/id/cs-17225. Published.

# Acknowledgements

I would first like to thank Allah Almighty Who empowered me with the devoting nature to carry out this work with full passion, enthusiasm and consistency. It is only because of His blessings that helped me to start over after every failure with a belief that *everything happens for a good reason*.

I would then like to express my sincere gratitude to my supervisor, Prof. Jan Madsen, who gave me an opportunity to work on such an interesting and emerging field of technology. The research carried out in this thesis would not have reached to this level without Jan's invaluable guidance, endless support, constructive feedbacks and time-to-time appreciations. I also thank him for encouraging and supporting me to attend relevant events to get myself updated with the ongoing research. I feel that I can never pay him back for his support and favors, but I will forever be grateful to him. I cannot imagine if there could be a better way of mentoring someone than how Jan supervised me. One day, when I will become a supervisor, I strongly believe that I will follow his example of mentorship - a courteous, humble and encouraging attitude which force students to continue working with their mentors passionately.

I further acknowledge Jan that he introduced me to many outstanding individuals in this field of research and I am thankful to all of them for their help. In particular, I would honestly like to thank Prof. Chris J. Myers for his constant support and help in clarifying my each and every confusion related to the topic. He not only helped me solving issues related to iBioSim tool, but also helped me getting my problems solved related to Cello tool. I also like to thank Prof. Douglas Densmore, for providing me an opportunity to work in CIDAR lab at Boston university as a visiting student. The ideas I gathered during this visit motivated me to work on design/synthesis field as well. I am also thankful to Dr. Nicholas Roehner for reviewing the derived relationship between real and simulation parameters; and Arash Khoshparvar for assisting me in solving issues related to SBOL-SBML conversion and providing me with the correct SBOL models of genetic circuits. Without these genetic circuit models, I could have never experimentally proved the concepts presented in this thesis.

In addition, I am greatly indebted to the wonderful staff and colleagues at DTU Compute, specifically Karin Tunder for her boundless help in administrative matters; Henning Christiansen from the IT department for his help in solving issues related to BDA-Compute web page; and DTU itself for supporting my research studies. Honestly, I have never experienced such a wonderful, wellorganized, respectable and a friendly working environment ever in my life before. I also like to thank my friends Qasim Rajpoot and Kamran Manzoor for their help in solving compiler-related issues.

I am also grateful to my parents and siblings for their support and love, specially to my father, Prof. Jawed Altaf Baig. I would not be a person I am today without his moral support and guidance in every walk of my life. Last but most important, I would like to thank my ever best friend and wife, Sumaiya Hasan, for her unconditional love and comfort she has given me specially during the whole span of my PhD research. I acknowledge that she had not only been patient with me during my hard times but also console me enormously to start over, after every failure, with new enthusiasm. My family has been a continuous source of my happiness and looking at them always motivated me to work harder for their good future as well. I am also grateful for Sumaiya's sacrifices she only made to take good care of our children (*Saleh and Nourah*), whenever I was away or busy in achieving hard deadlines and project goals. Without any hesitations, I can say that she had struggled equally to help me accomplish this lifetime achievement.

### Contents

| Sι       | Summary (English)   |                                                      |     |  |  |  |

|----------|---------------------|------------------------------------------------------|-----|--|--|--|

| Sι       | ummary (Danish) iii |                                                      |     |  |  |  |

| Pı       | reface v            |                                                      |     |  |  |  |

| R        | esear               | ch Dissemination                                     | vii |  |  |  |

| A        | cknov               | wledgements                                          | ix  |  |  |  |

| 1        | Intr                | oduction                                             | 1   |  |  |  |

|          | 1.1                 | Why computations in cells?                           | 2   |  |  |  |

|          | 1.2                 | State-of-the-art                                     | 2   |  |  |  |

|          | 1.3                 | Motivation                                           | 3   |  |  |  |

|          | 1.4                 | Present Challenges                                   | 4   |  |  |  |

|          |                     | 1.4.1 Virtual experimentation                        | 4   |  |  |  |

|          |                     | 1.4.2 Timing and threshold analysis                  | 5   |  |  |  |

|          |                     | 1.4.3 Automatic logic validation                     | 5   |  |  |  |

|          |                     | 1.4.4 Effortless circuit designing                   | 6   |  |  |  |

|          | 1.5                 | Thesis Contributions                                 | 6   |  |  |  |

|          | 1.6                 | Thesis Organization                                  | 8   |  |  |  |

| <b>2</b> | Ger                 | etic Circuits                                        | 11  |  |  |  |

|          | 2.1                 | Central Dogma of Molecular Biology                   | 12  |  |  |  |

|          | 2.2                 | Example Genetic Circuit: Lac Operon                  | 14  |  |  |  |

|          |                     | 2.2.1 Genetic logic in lac operon                    | 16  |  |  |  |

|          |                     | 2.2.2 The standard SBOL representation of lac operon | 16  |  |  |  |

|          | 2.3                 | Standards                                            | 17  |  |  |  |

|          | 2.4                 | Genetic Design Automation (GDA) Tools                | 19  |  |  |  |

|          |     | 2.4.1   | Sequence editing tools                                                         | 20 |

|----------|-----|---------|--------------------------------------------------------------------------------|----|

|          |     | 2.4.2   | Biochemical modeling and design composition tools                              | 20 |

|          |     | 2.4.3   | Genetic mapping tools                                                          | 22 |

| 3        | Dyı | namic   | Virtual Analyzer and Simulator ( <i>D-VASim</i> )                              | 23 |

|          | 3.1 | Motiv   | ation                                                                          | 24 |

|          | 3.2 | Metho   | bodology and Experimental Approach                                             | 25 |

|          |     | 3.2.1   | SBML support                                                                   | 27 |

|          |     | 3.2.2   | Virtual instrumentation                                                        | 27 |

|          |     | 3.2.3   | Virtual experimentation                                                        | 30 |

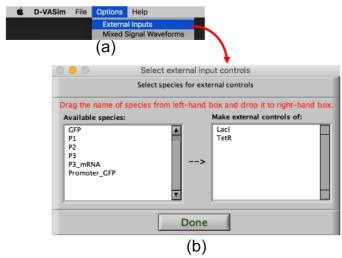

|          |     | 3.2.4   | Logic verification and timing analysis                                         | 31 |

|          | 3.3 | Discu   | ssion                                                                          | 31 |

| <b>4</b> | Ger | netic C | Circuits Timing Analysis                                                       | 33 |

|          | 4.1 | Metho   | odology                                                                        | 34 |

|          |     | 4.1.1   | Preliminary analysis of threshold value                                        | 36 |

|          |     | 4.1.2   | Preliminary analysis of propagation delay                                      | 38 |

|          |     | 4.1.3   | D-VASim plug-in for threshold value and propagation de-                        |    |

|          |     |         | lay analyses                                                                   | 39 |

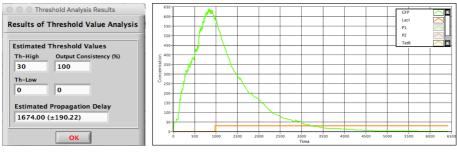

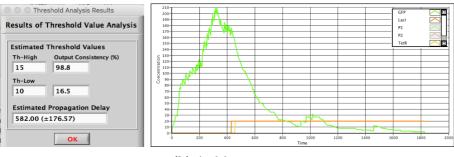

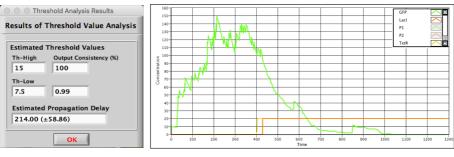

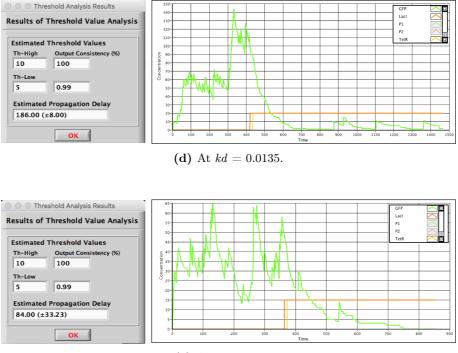

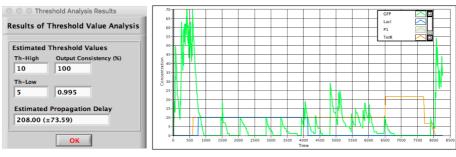

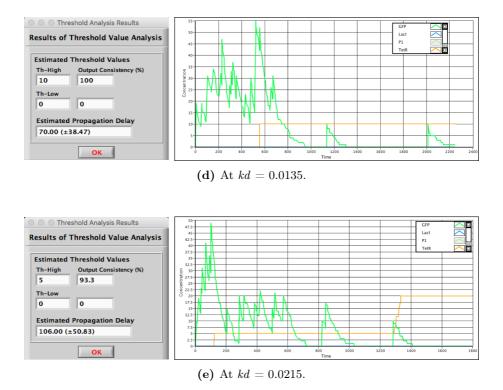

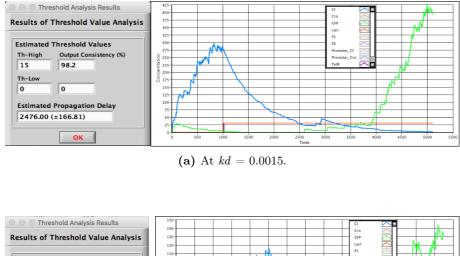

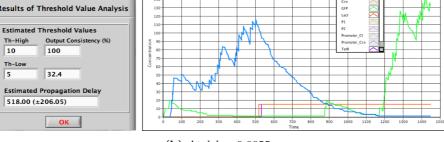

|          | 4.2 | Exper   | imentation by Simulation                                                       | 45 |

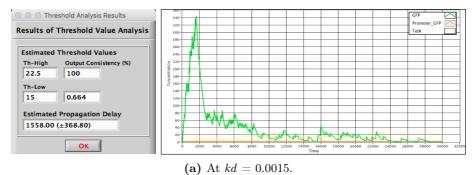

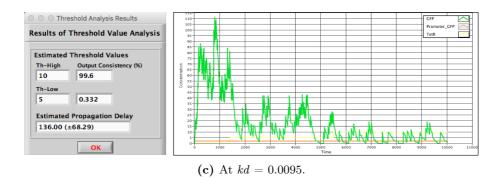

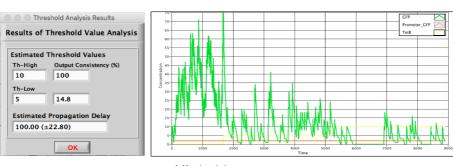

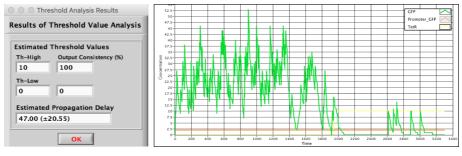

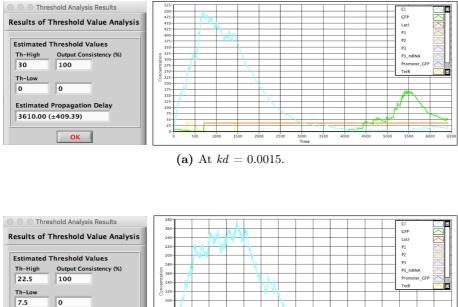

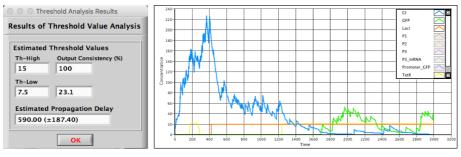

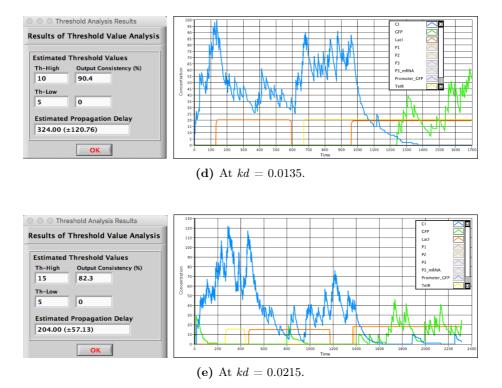

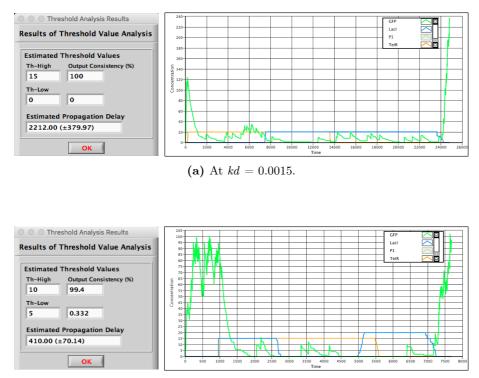

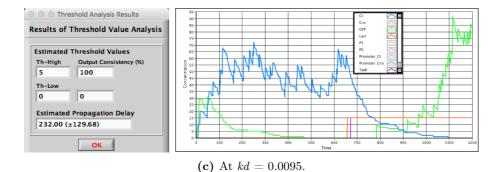

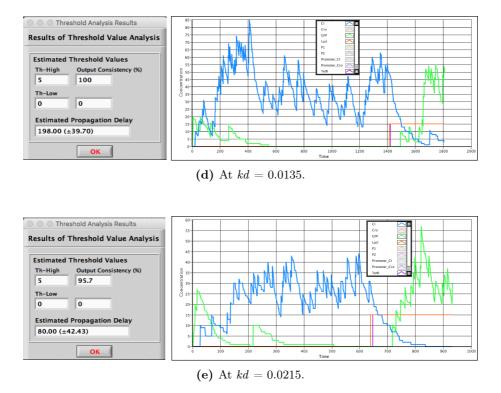

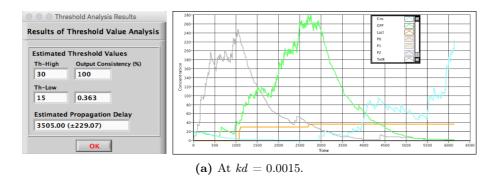

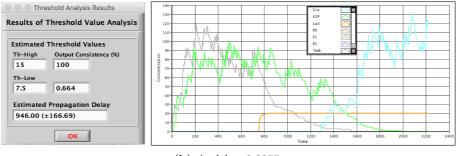

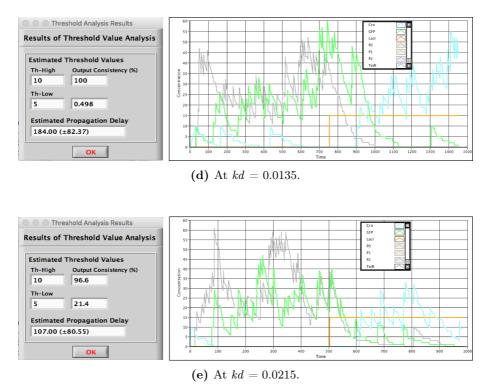

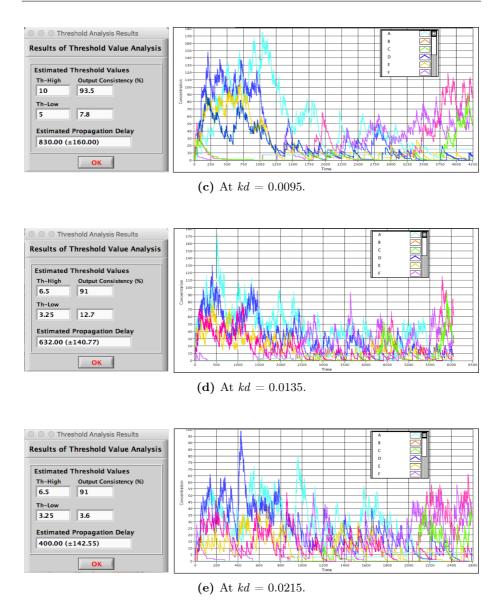

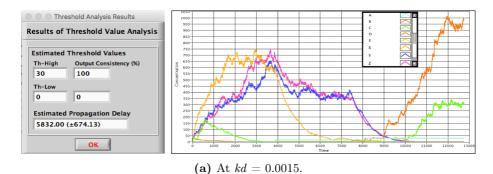

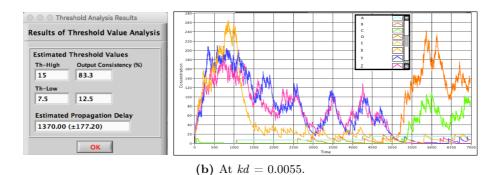

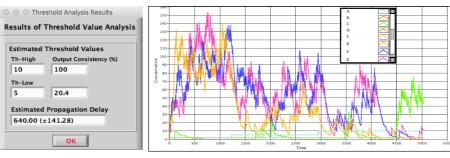

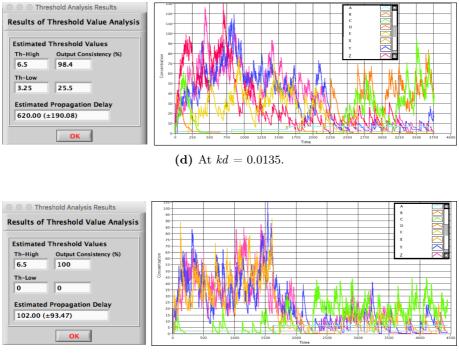

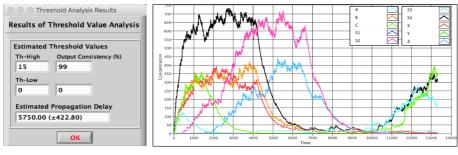

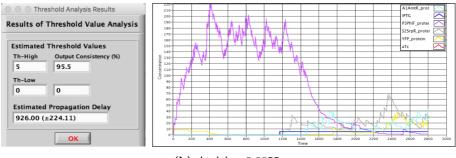

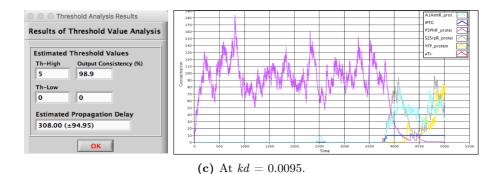

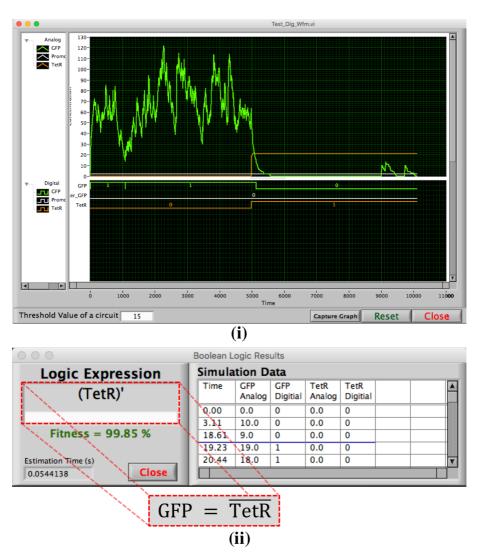

|          |     | 4.2.1   | Effects of varying $kd$ on the threshold values and propa-                     |    |

|          |     |         | gation delays                                                                  | 49 |

|          |     | 4.2.2   | Effects of varying threshold values on the propagation delays                  | 49 |

|          |     | 4.2.3   | Effects of varying threshold values on the $\%$ output con-                    |    |

|          |     |         | sistency at high $kd$                                                          | 51 |

|          |     | 4.2.4   | Other parameters effecting the threshold values                                | 51 |

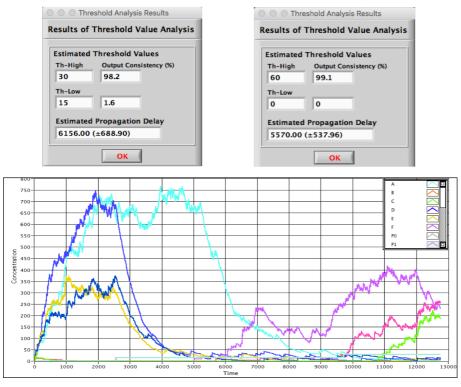

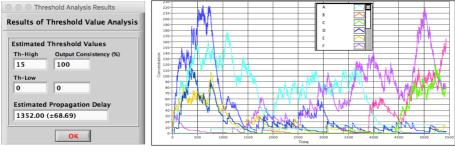

|          |     | 4.2.5   | Intermediate propagation delays                                                | 52 |

|          |     | 4.2.6   | Experimentation on the SBML model of real genetic circuit                      |    |

|          | 4.3 | Discu   | ssion                                                                          | 54 |

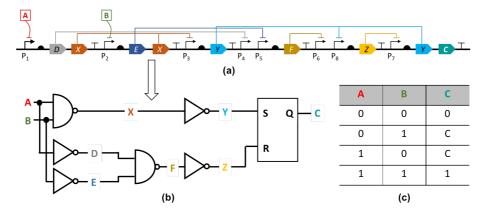

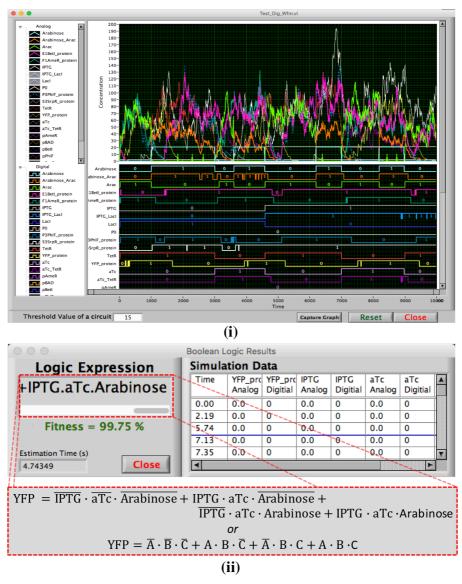

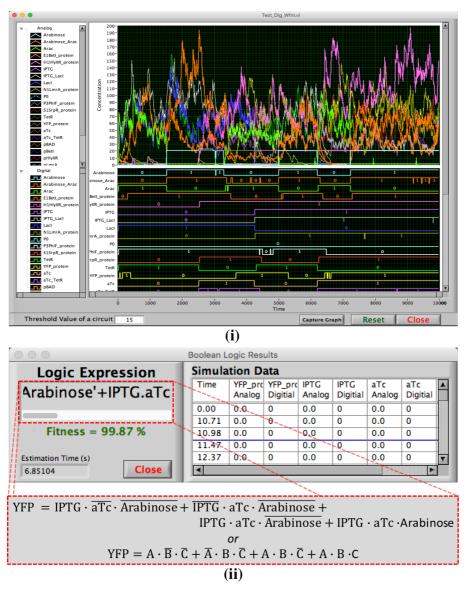

| <b>5</b> | Ger |         | Circuits Logic Analysis                                                        | 57 |

|          | 5.1 |         | odology                                                                        | 58 |

|          |     | 5.1.1   | Overview                                                                       | 58 |

|          |     | 5.1.2   | Input combinations analysis                                                    | 60 |

|          |     | 5.1.3   | Variation analysis and Boolean expression construction $% \mathcal{A}$ .       | 62 |

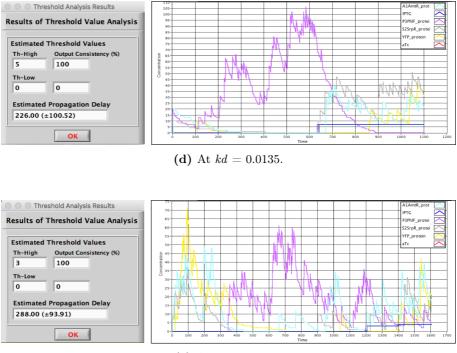

|          | 5.2 | Exper   | imentation by Simulation                                                       | 67 |

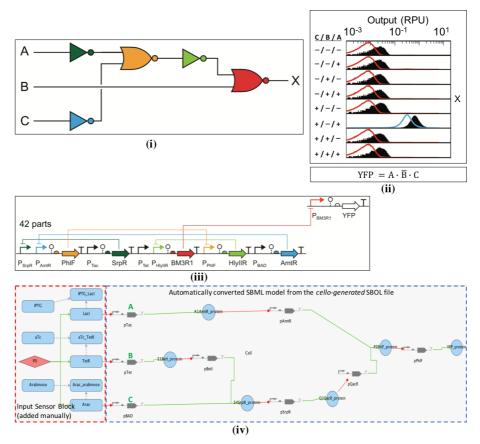

|          |     | 5.2.1   | $\label{eq:analysis} Analysis of the SBOL-SBML converted genetic circuit mod-$ |    |

|          |     |         | els                                                                            | 67 |

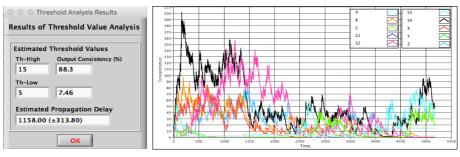

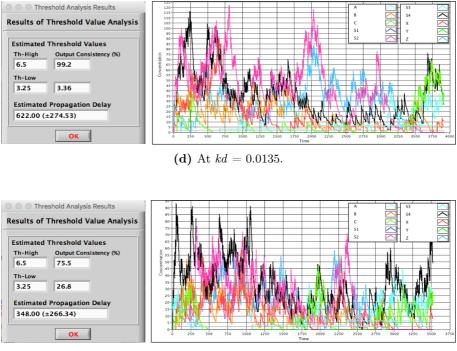

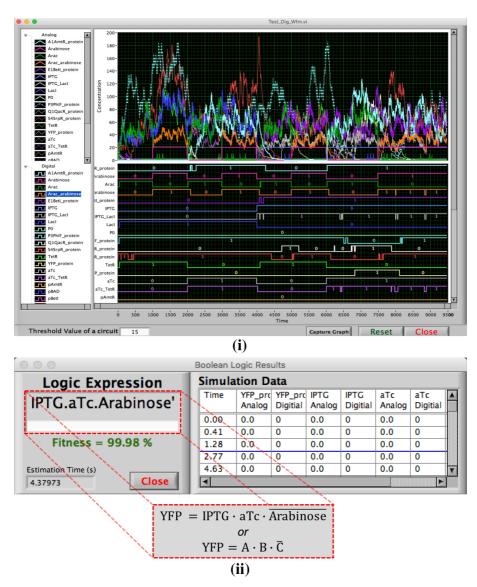

|          |     | 5.2.2   | Logic analysis and verification                                                | 70 |

|          |     | 5.2.3   | Effects of varying threshold value on circuit's behavior                       | 73 |

|          |     | 5.2.4   | Performance analysis                                                           | 74 |

|          | 5.3 | Discu   | ssion                                                                          | 75 |

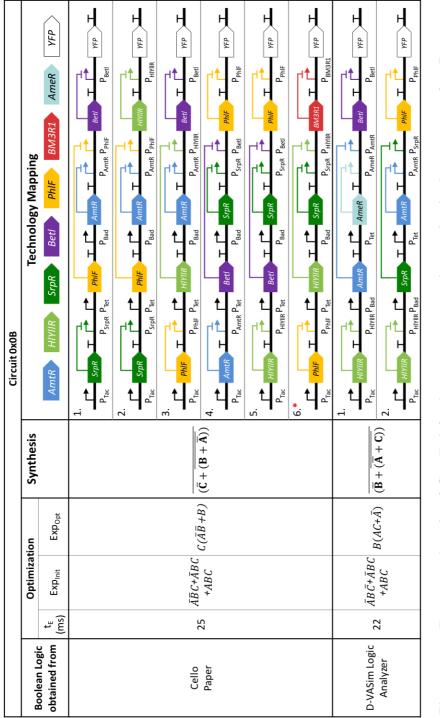

| 6            | Gen            | ne Tech – A Technology Mapping Tool for Genetic Circuits    | 77  |

|--------------|----------------|-------------------------------------------------------------|-----|

|              | 6.1            | Motivation                                                  | 78  |

|              | 6.2            | Methodology                                                 | 81  |

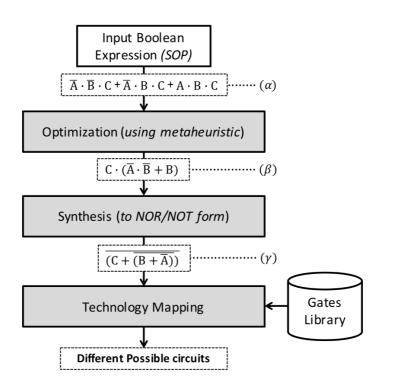

|              |                | 6.2.1 Logic optimization                                    | 82  |

|              |                | 6.2.2 Logic synthesis                                       | 86  |

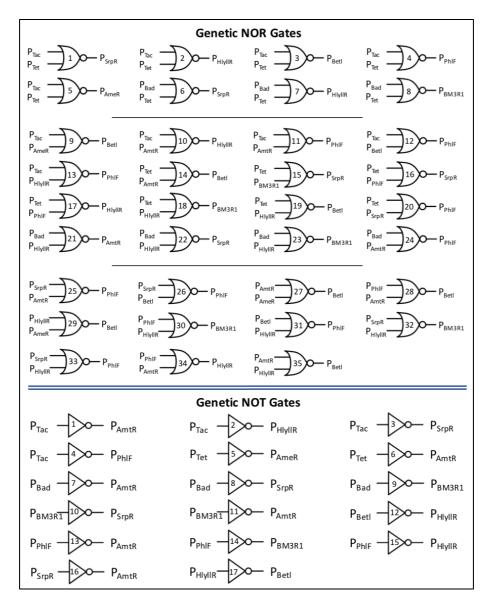

|              |                | 6.2.3 Genetic technology mapping                            | 88  |

|              | 6.3            | Experimentation by Simulation                               | 94  |

|              | 6.4            | Discussion                                                  | 97  |

| 7            | Par            | ameter Estimation and Sensitivity Analysis                  | 99  |

|              | 7.1            | Statistical Model Checking with Uppaal                      | 100 |

|              |                | 7.1.1 Methodology                                           | 101 |

|              |                | 7.1.2 Role of D-VASim in model checking                     | 101 |

|              |                | 7.1.3 Experimentation by Simulation                         | 103 |

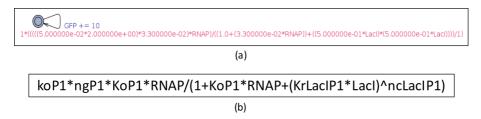

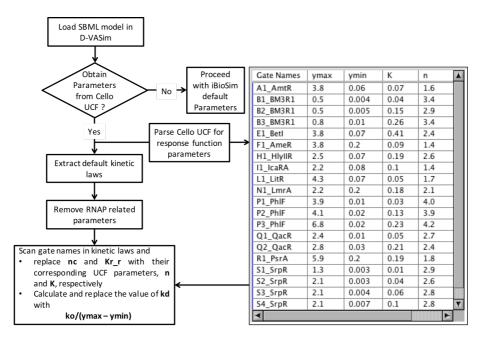

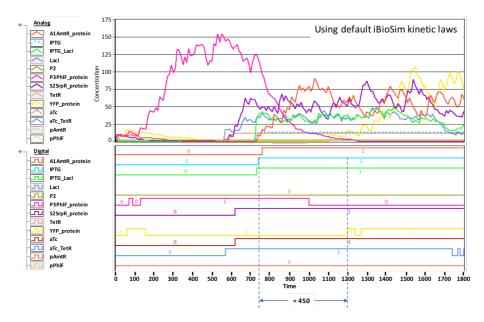

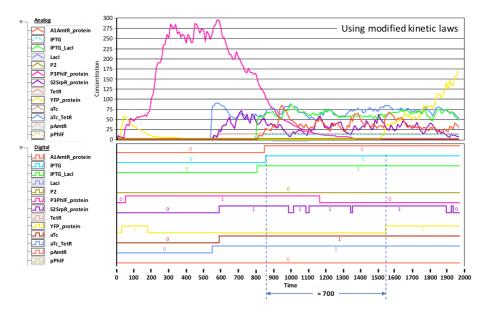

|              | 7.2            | Semi-realistic Simulation with Cello UCF parameters         | 108 |

|              |                | 7.2.1 Relation between iBioSim default parameters and Cello |     |

|              |                | response parameters                                         | 109 |

|              |                | 7.2.2 Modification of kinetic laws in D-VASim               |     |

|              |                | 7.2.3 Experimentation by Simulation                         |     |

|              | 7.3            | Discussion                                                  | 117 |

| 8            | Con            | clusions and Future Work                                    | 119 |

|              | 8.1            | Summary and Conclusions                                     | 119 |

|              | 8.2            | Research Impact                                             |     |

|              | 8.3            | Future Work                                                 |     |

|              |                | 8.3.1 Extension from an experimental viewpoint              | 122 |

|              |                | 8.3.2 Extension from an implementation viewpoint            | 123 |

| Bi           | bliog          | graphy                                                      | 125 |

|              | -              |                                                             |     |

| Aj           | ppen           | dices                                                       | 133 |

| $\mathbf{A}$ | D-V            | VASim – Supplementary Data                                  | 135 |

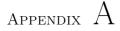

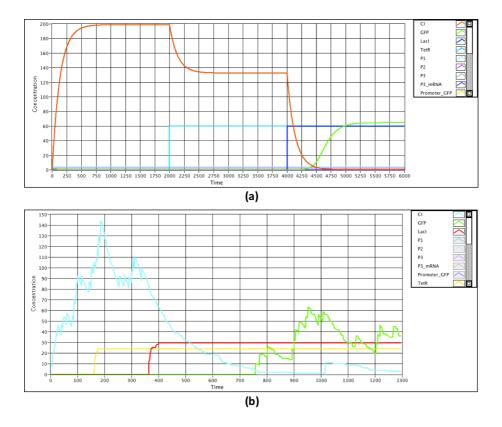

|              | A.1            | ODE and Stochastic Simulation Results                       | 135 |

| В            | $\mathbf{Tim}$ | ning Analysis – Supplementary Data                          | 141 |

|              |                | Ckt 1 – NOT gate                                            | 141 |

|              |                | Ckt 2 – NAND gate                                           |     |

|              |                | Ckt 3 – AND gate                                            |     |

|              | B.4            | Ckt 4 – NOR gate                                            | 148 |

|              | B.5            | Ckt 5 – OR gate                                             | 150 |

|              | B.6            | Ckt 6 – Delay Circuit                                       | 152 |

|              | B.7            | Ckt 7 – Toggle Muller C-Element                             | 154 |

|              | B.8            | Ckt 8 – Majority Muller C Element                           | 156 |

|              | B.9            | Ckt 9 – Speed Independent Muller C Element                  | 158 |

|              | B.10 | Ckt $10$ | – Real Genetic AND Gate                               | 160 |

|--------------|------|----------|-------------------------------------------------------|-----|

| $\mathbf{C}$ | Log  | ic Anal  | lysis – Supplementary Data                            | 163 |

|              | C.1  | Experi   | mentation on the Genetic Circuit Models from U-Utah   | 163 |

|              |      | C.1.1    | NOT gate circuit                                      | 164 |

|              |      | C.1.2    | NOR gate circuit                                      | 166 |

|              |      | C.1.3    | NAND gate circuit                                     | 168 |

|              |      | C.1.4    | OR gate circuit                                       | 170 |

|              |      | C.1.5    | AND gate circuit                                      | 172 |

|              | C.2  | Experi   | mentation on the Genetic Circuit Models from MIT & BU | 174 |

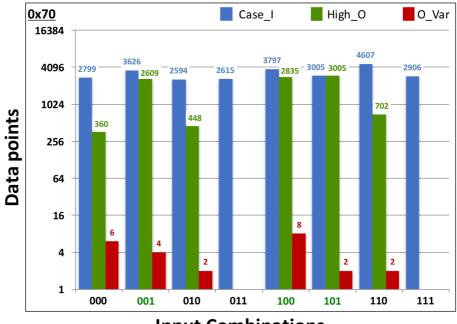

|              |      | C.2.1    | Genetic circuit $0x70$                                | 175 |

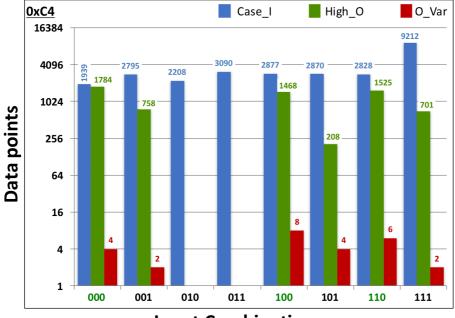

|              |      | C.2.2    | Genetic circuit 0xC4                                  | 178 |

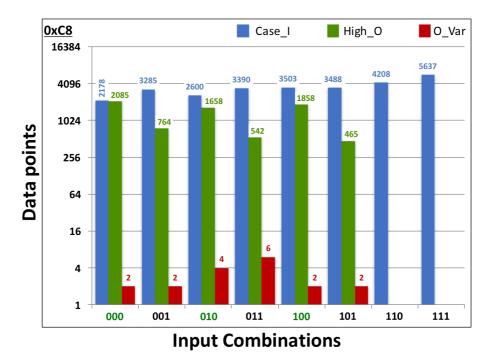

|              |      | C.2.3    | Genetic circuit 0xC8                                  | 181 |

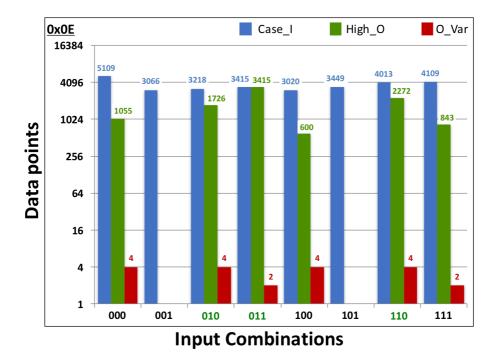

|              |      | C.2.4    | Genetic circuit $0x0E$                                | 184 |

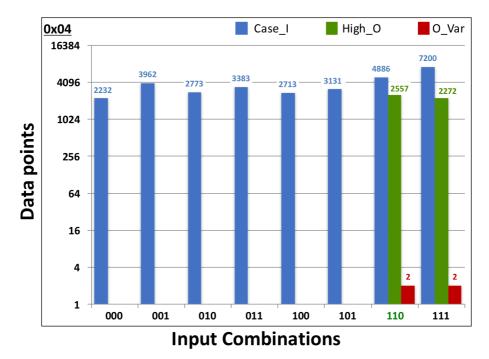

|              |      | C.2.5    | Genetic circuit 0x04                                  | 187 |

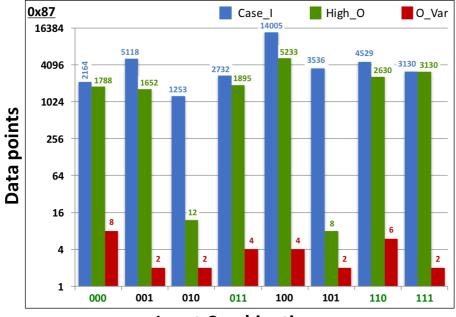

|              |      | C.2.6    | Genetic circuit 0x87                                  | 190 |

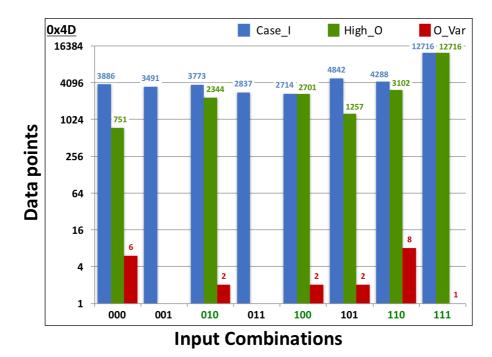

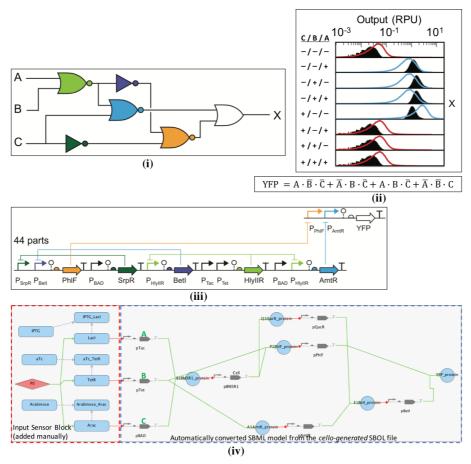

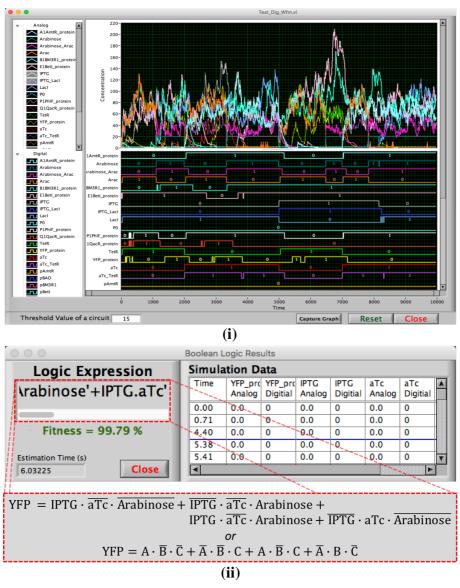

|              |      | C.2.7    | Genetic circuit 0x4D                                  | 193 |

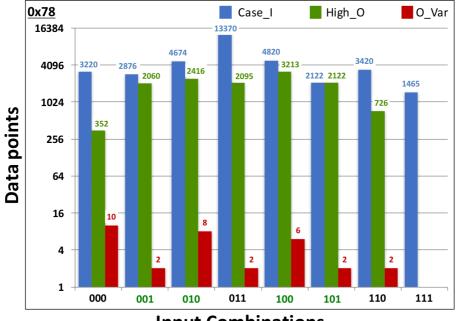

|              |      | C.2.8    | Genetic circuit 0x78                                  | 196 |

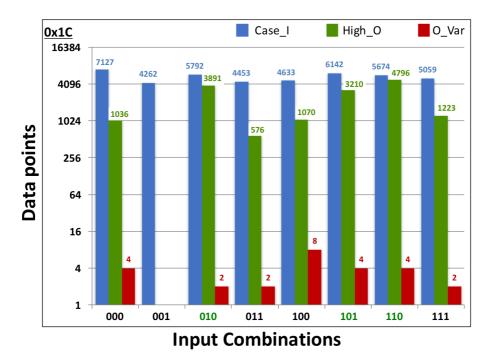

|              |      | C.2.9    | Genetic circuit 0x1C                                  | 199 |

|              |      | C.2.10   | Discussion                                            | 202 |

| D            | Gen  | eTech    | - Supplementary Data                                  | 203 |

| $\mathbf{E}$ | D-V  | ASim     | – Quick Start Guide                                   | 209 |

## List of Figures

| 1.1 | Thesis abstract diagram                                             | 8  |

|-----|---------------------------------------------------------------------|----|

| 2.1 | The hierarchical relationship of living cell and gene.              | 12 |

| 2.2 | The process of transcription.                                       | 13 |

| 2.3 | Transcriptional regulation of lac operon                            | 14 |

| 2.4 | Genetic logic in lac operon.                                        | 16 |

| 2.5 | SBOL visual representation (or SBOLv) of lac operon genetic         |    |

|     | system.                                                             | 17 |

| 2.6 | SBML and SBOLv diagram of genetic AND gate                          | 18 |

| 2.7 | Cropped images of SBML and SBOL files                               | 19 |

| 3.1 | Simulation flow of D-VASim.                                         | 26 |

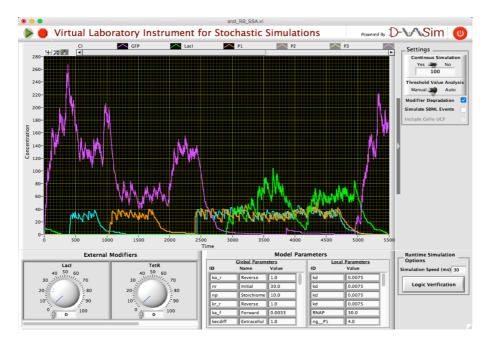

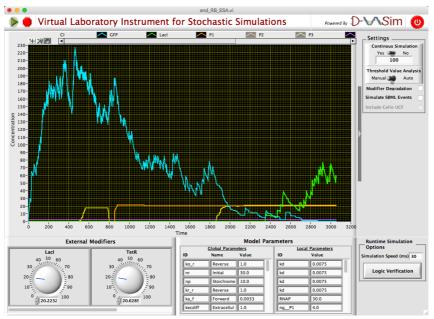

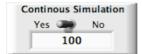

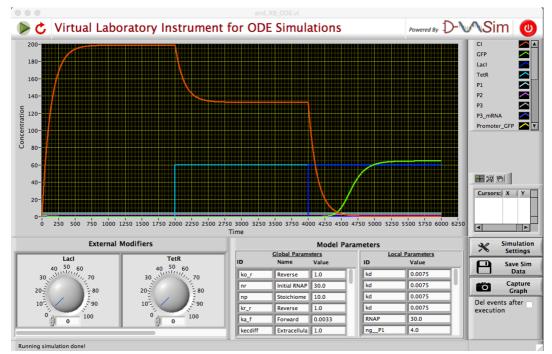

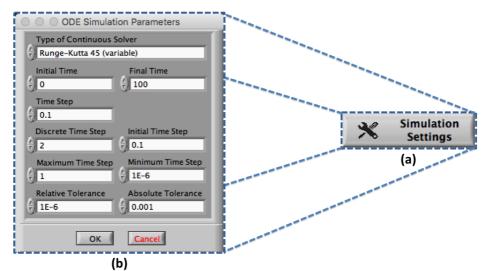

| 3.2 | D-VASim main interface.                                             | 27 |

| 3.3 | Virtual instrument for stochastic simulations                       | 28 |

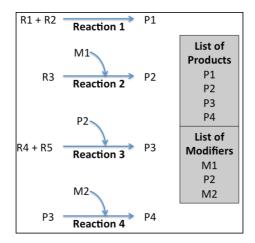

| 3.4 | Example reactions for identifying external modifiers                | 29 |

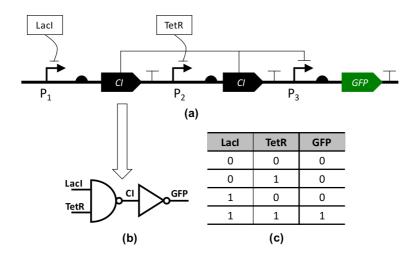

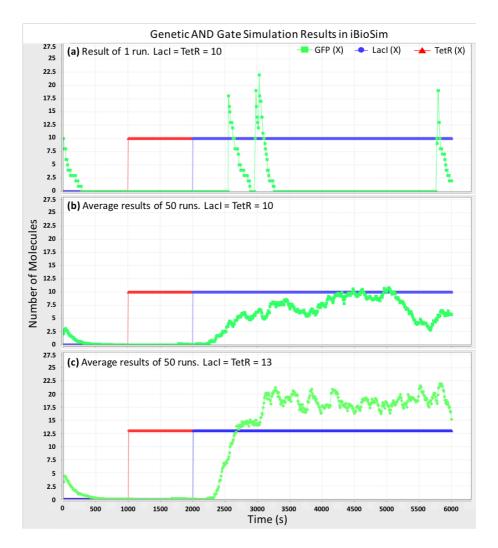

| 3.5 | Genetic AND gate circuit.                                           | 30 |

| 4.1 | Preliminary analysis of a threshold value.                          | 37 |

| 4.2 | Preliminary analysis of a propagation delay                         | 38 |

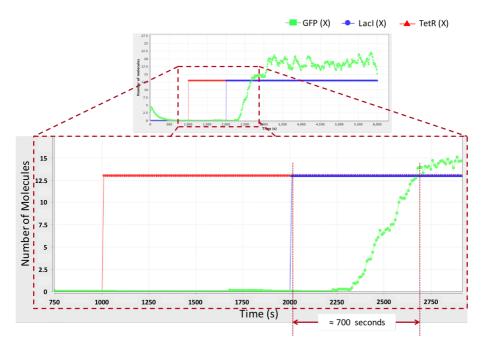

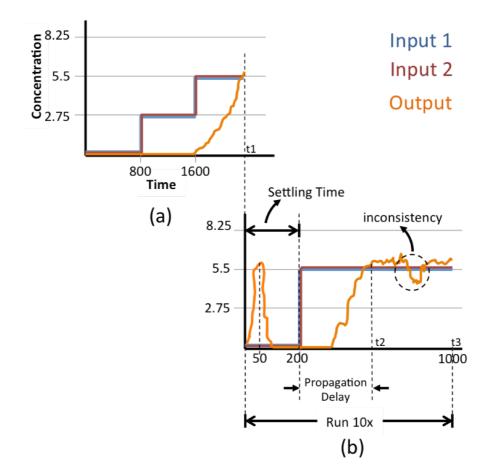

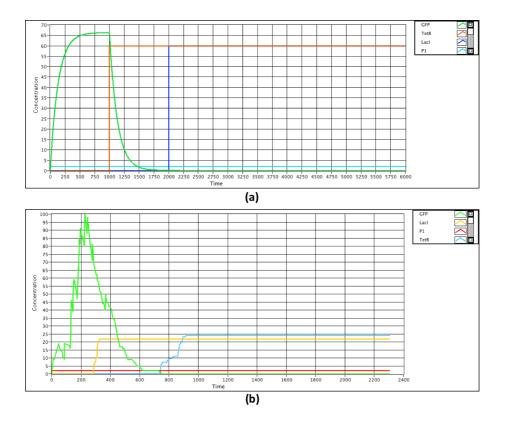

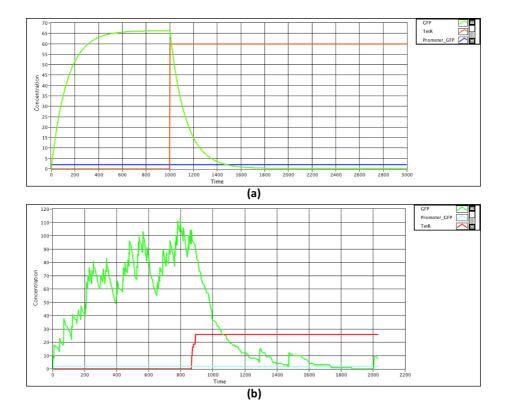

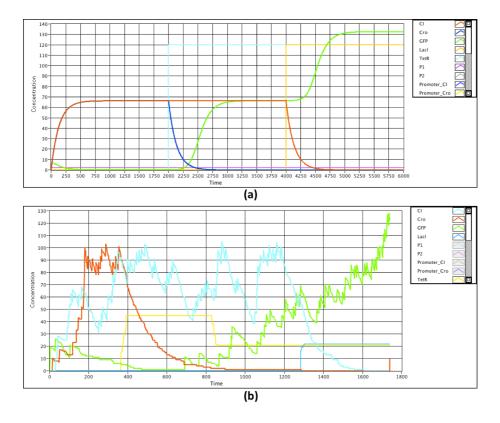

| 4.3 | Sample time scale plots of the genetic AND gate                     | 43 |

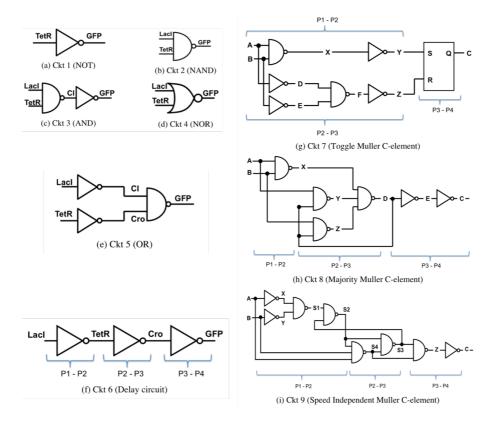

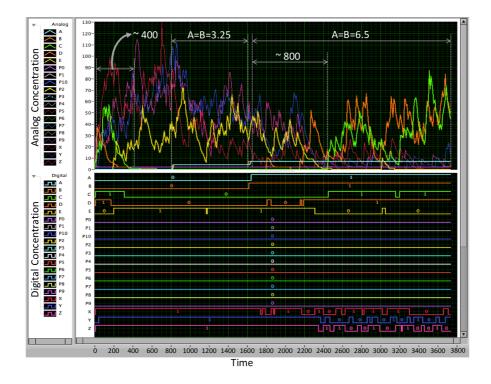

| 4.4 | Experimental genetic circuits for timing analysis                   | 46 |

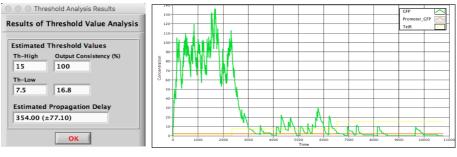

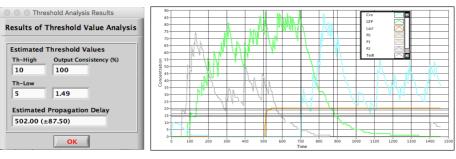

| 4.5 | Results of threshold value and propagation delay analysis           | 47 |

| 4.6 | Analog and digital simulation traces of Ckt 8                       | 48 |

| 4.7 | Effects of varying degradation rate $(kd)$ on the propagation delay |    |

|     | of genetic logic circuits.                                          | 50 |

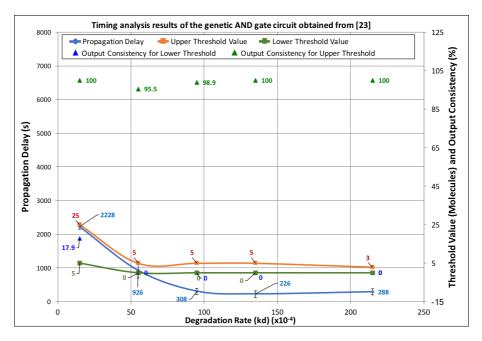

| 4.8 | SBML design of the genetic AND gate circuit                         | 54 |

| 4.9 | Effects of varying $kd$ on the SBML model of a real genetic AND     |    |

|     | gate                                                                | 55 |

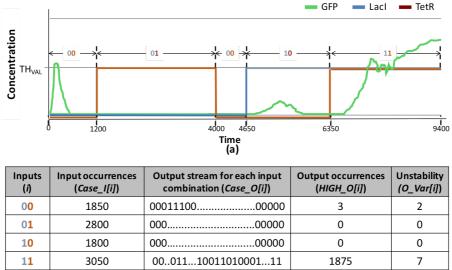

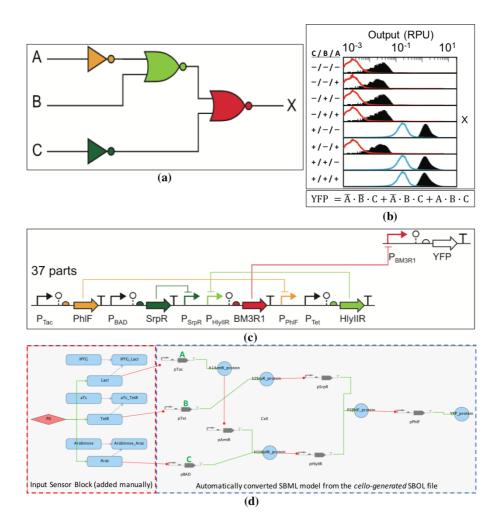

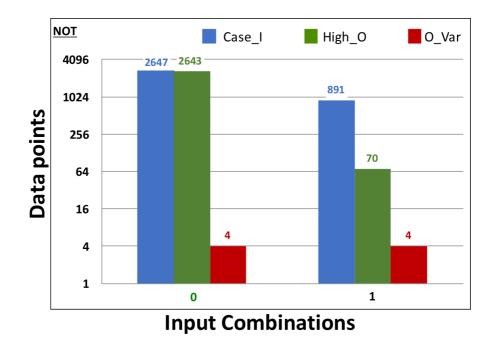

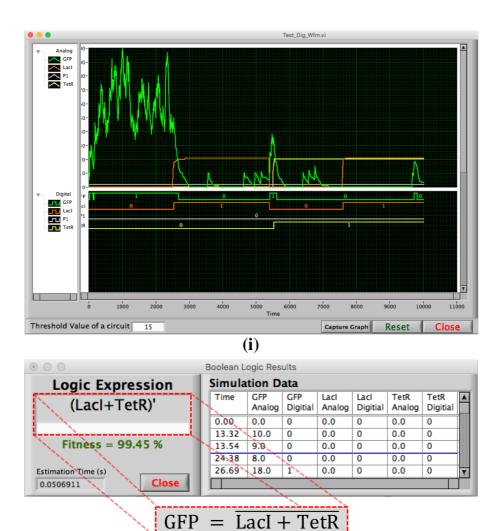

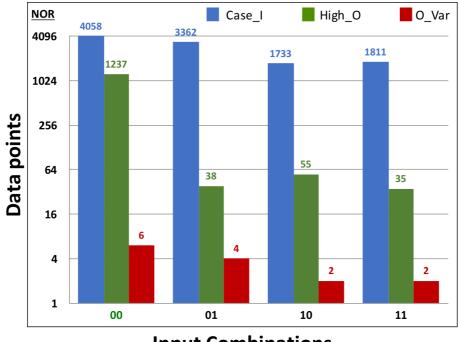

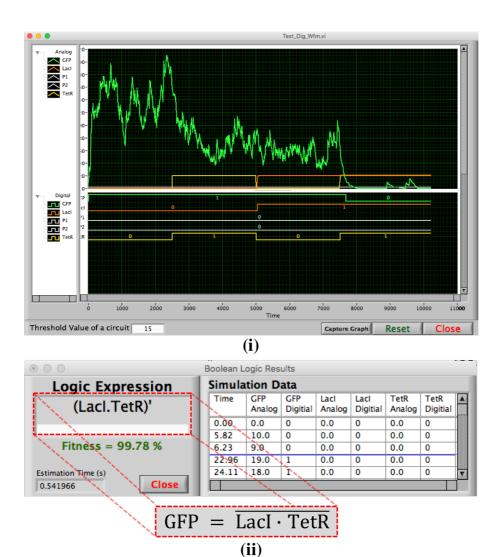

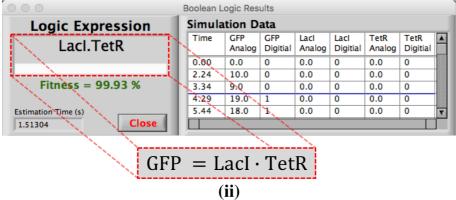

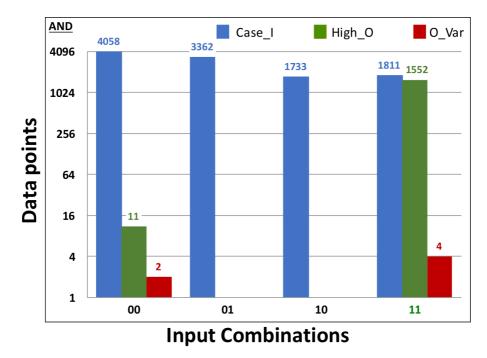

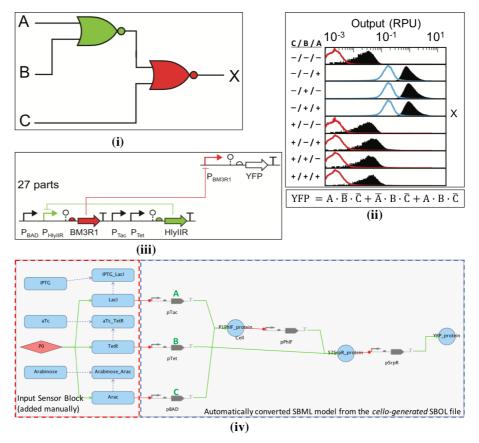

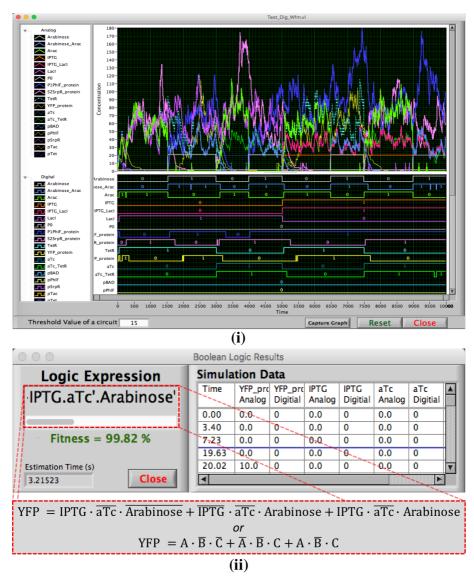

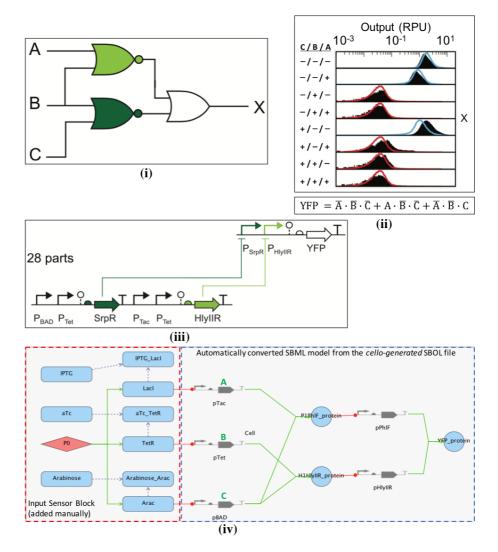

| 5.1         |                                                                         | 1  |

|-------------|-------------------------------------------------------------------------|----|

| 5.2         | Effectiveness of filtration process                                     | 5  |

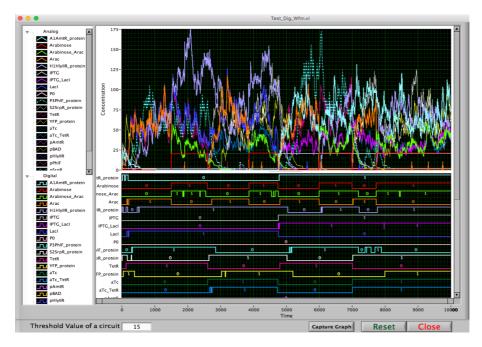

| 5.3         |                                                                         | 8  |

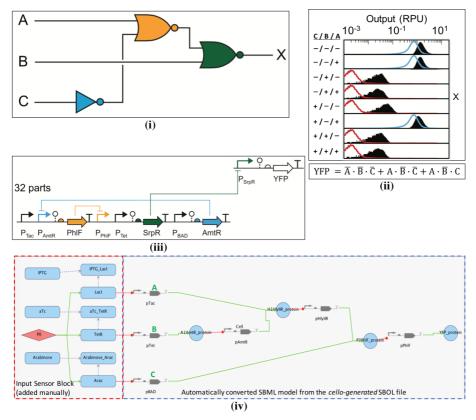

| 5.4         | Interactive simulation of 0x0B for logic analysis                       | 0  |

| 5.5         |                                                                         | 1  |

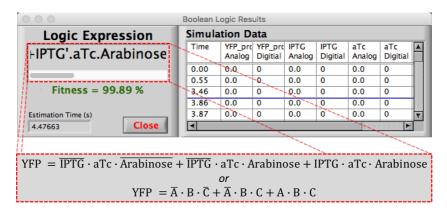

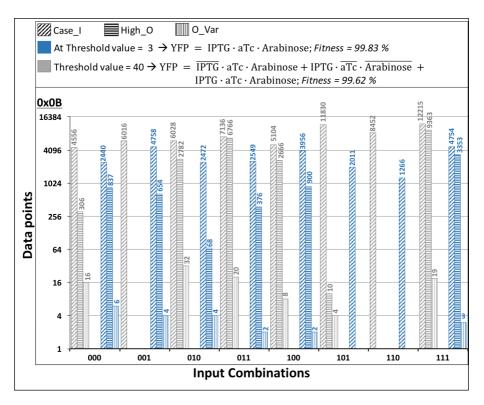

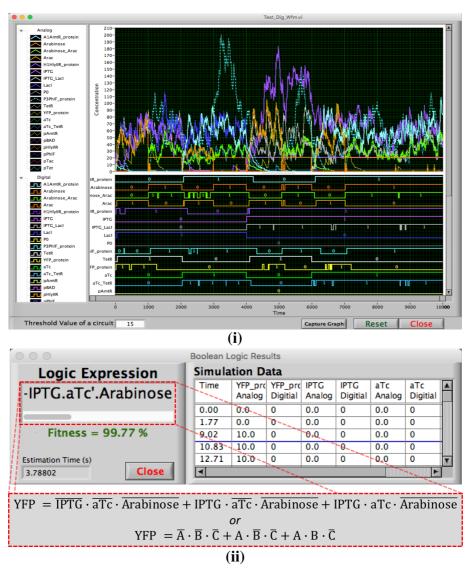

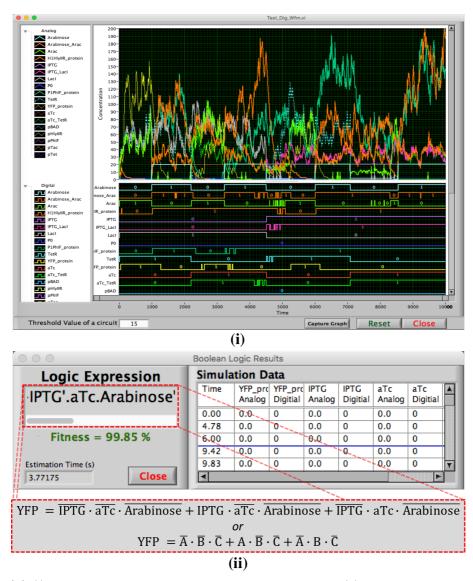

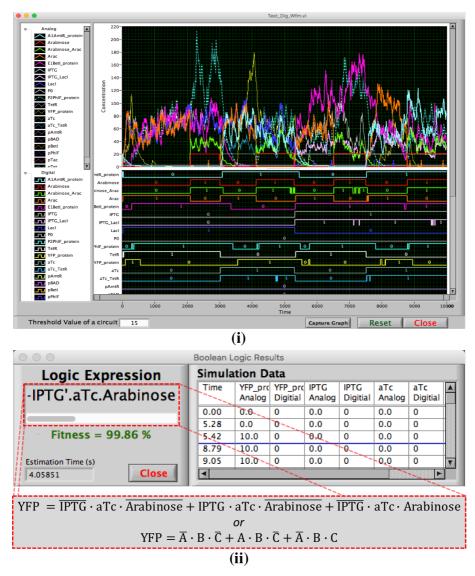

| 5.6         | Analytical simulation data of genetic circuit model 0x0B 7              | 2  |

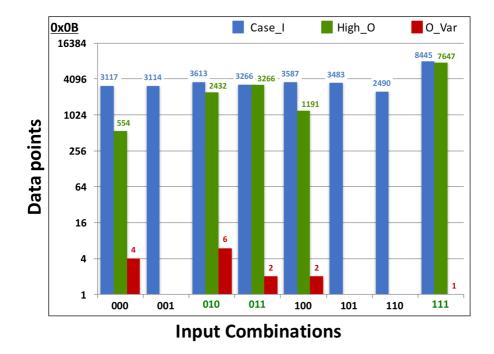

| 5.7         | Analytical data of circuit 0x0B for threshold values 3 and 40 7         | 3  |

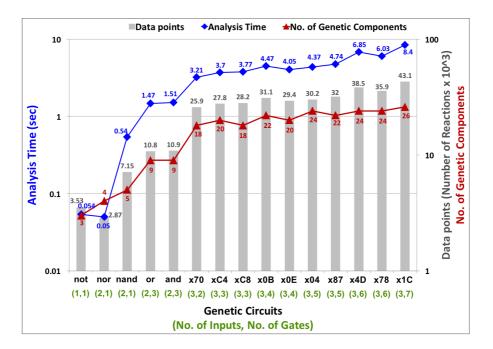

| 5.8         | Performance evaluation of the proposed algorithm                        | 5  |

|             |                                                                         |    |

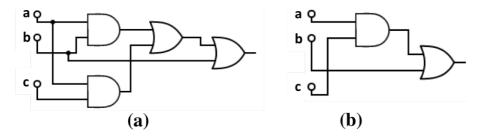

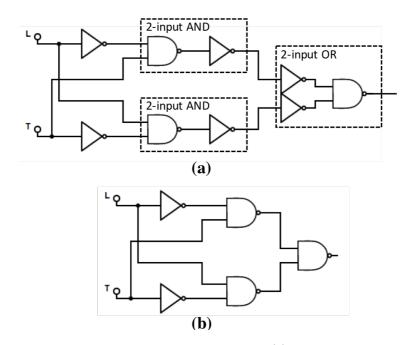

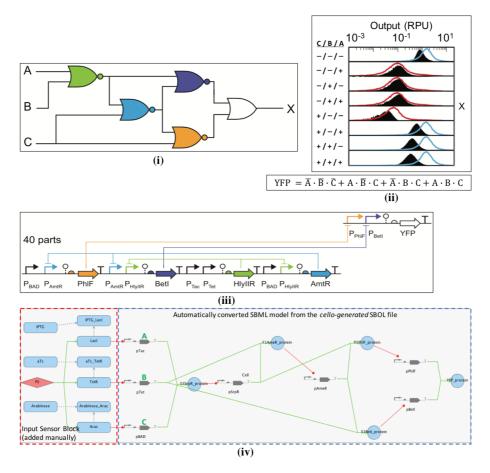

| 6.1         | 1 0 1                                                                   | 8  |

| 6.2         | 0                                                                       | 9  |

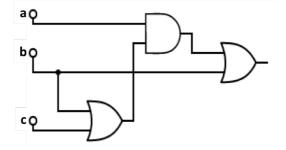

| 6.3         | <u> </u>                                                                | 0  |

| 6.4         |                                                                         | 51 |

| 6.5         | 1 1                                                                     | 5  |

| 6.6         | 1 1 0                                                                   | 8  |

| 6.7         | 0                                                                       | 9  |

| 6.8         | 8                                                                       | 0  |

| 6.9         | 1 1 1 0 0                                                               | 1  |

|             | 0                                                                       | 2  |

|             | 1 0 1                                                                   | 4  |

| 6.12        | Experimental results of technology mapping of $0x0B$ circuit 9          | 6  |

| 71          | En sin sut d'an efen et sin sit a del de din en dessification 10        | 0  |

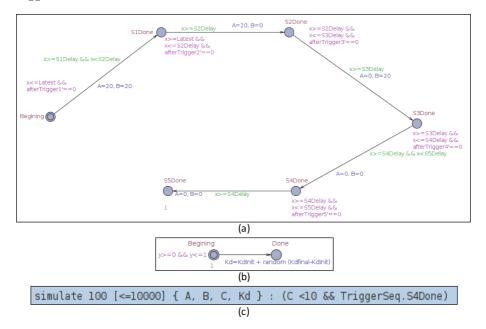

| 7.1         | Experimental flow of genetic circuit model checking and verification.10 |    |

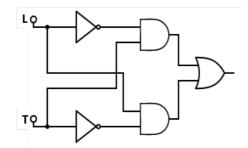

| 7.2         | Genetic toggle muller-C element                                         |    |

| 7.3         | Automaton to produce GFP in NAND gate                                   |    |

| 7.4         | The process automaton for triggering inputs in Uppaal 10                |    |

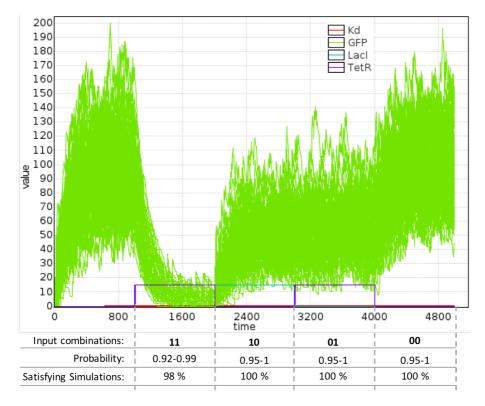

| 7.5         | SMC results of genetic NAND gate in Uppaal                              |    |

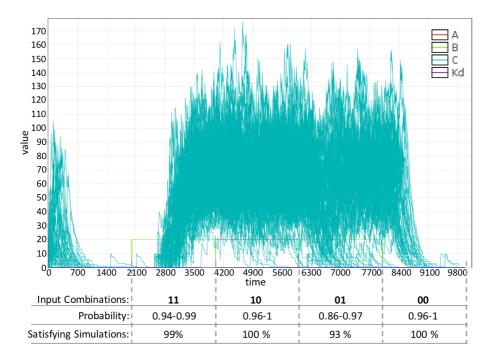

| 7.6         | SMC results of genetic toggle muller-C element in Uppaal 10             |    |

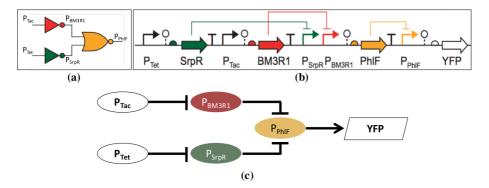

| 7.7         | The schematic and simplified model of a genetic AND gate 11             |    |

| 7.8         | SBML design of the genetic AND gate circuit                             |    |

| 7.9         | The default and modified kinetic laws of genetic AND gate model. 11     |    |

| 7.10        | The integration flow of Cello UCF parameters and D-VASim 11             | 5  |

| 7.11        | D-VASim simulation plots of the AND gate, using the default             | ~  |

| <b>H</b> 10 | kinetic laws of iBioSim                                                 | 6  |

| 7.12        | D-VASim simulation plots of the AND gate, using the modified            | -  |

|             | kinetic laws                                                            | 1  |

| 8.1         | D-VASim download metrics                                                | 2  |

| A.1         | Simulation of genetic AND gate circuit                                  | e  |

|             | · ·                                                                     |    |

| A.2         | 0                                                                       |    |

| A.3         | Simulation of genetic NOR gate circuit                                  |    |

| A.4         | Simulation of genetic NOT gate circuit                                  |    |

| A.5         | Simulation of genetic OR gate circuit                                   | U  |

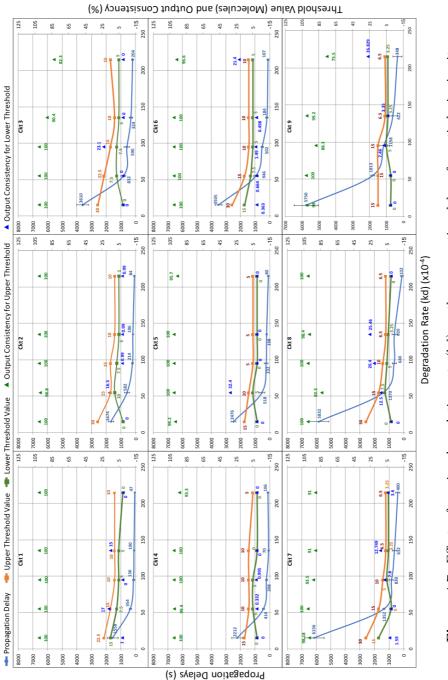

| B.1  | Timing analysis results of Ckt 1 - NOT gate.                  | 143 |

|------|---------------------------------------------------------------|-----|

| B.2  | Timing analysis results of Ckt 2 - NAND gate.                 |     |

| B.3  | Timing analysis results of Ckt 3 - AND gate.                  |     |

| B.4  | Timing analysis results of Ckt 4 - NOR gate.                  |     |

| B.5  | Timing analysis results of Ckt 5 - OR gate.                   |     |

| B.6  | Timing analysis results of Ckt 6 - Delay circuit.             |     |

| B.7  | Timing analysis results of Ckt 7 - Toggle Muller C-Element.   |     |

| B.8  | Timing analysis results of Ckt 8 - Majority Muller C Element. |     |

| B.9  | Timing analysis results of Ckt 9 - Speed Independent Muller C |     |

|      | Element.                                                      | 159 |

| B.10 | Timing analysis results of Ckt 10 - Real genetic AND gate     |     |

|      |                                                               |     |

| C.1  | Simulation and logic analysis of the genetic NOT circuit      |     |

| C.2  | Simulation and logic analysis of the genetic NOR circuit      | 167 |

| C.3  | Simulation and logic analysis of the genetic NAND circuit     | 169 |

| C.4  | Simulation and logic analysis of the genetic OR circuit.      | 171 |

| C.5  | Simulation and logic analysis of the genetic AND circuit      | 173 |

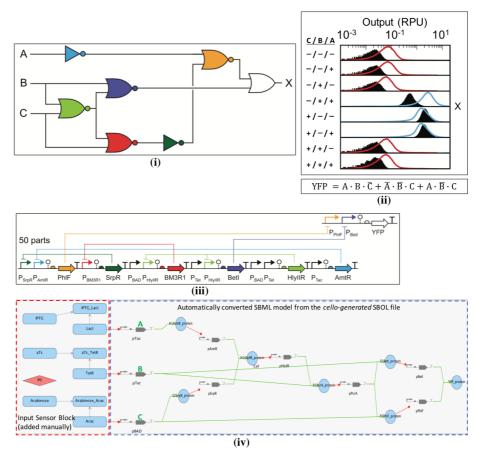

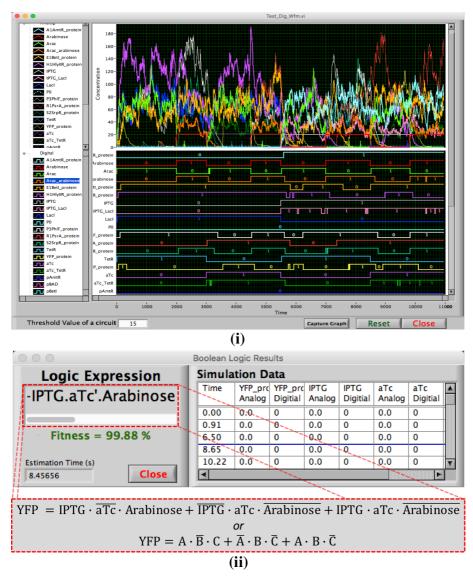

| C.6  | Simulation and logic analysis of the genetic $0x70$ circuit   | 177 |

| C.7  | Simulation and logic analysis of the genetic 0xC4 circuit     | 180 |

| C.8  | Simulation and logic analysis of the genetic 0xC8 circuit     | 183 |

| C.9  | Simulation and logic analysis of the genetic 0x0E circuit     | 186 |

| C.10 | Simulation and logic analysis of the genetic 0x04 circuit     | 189 |

| C.11 | Simulation and logic analysis of the genetic 0x87 circuit     | 192 |

| C.12 | Simulation and logic analysis of the genetic 0x4D circuit     | 195 |

| C.13 | Simulation and logic analysis of the genetic 0x78 circuit     | 198 |

| C.14 | Simulation and logic analysis of the genetic 0x1C circuit     | 201 |

|      |                                                               |     |

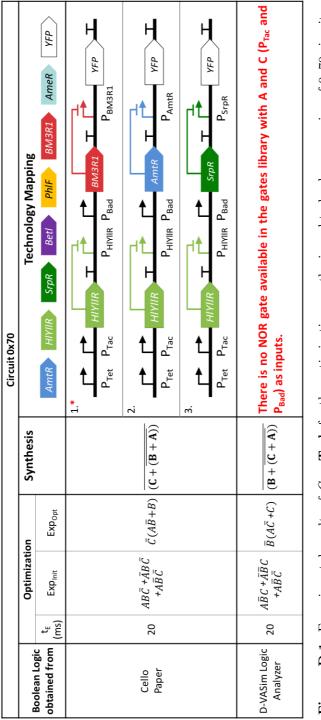

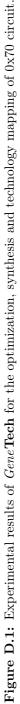

| D.1  | Experimental results of technology mapping of 0x70 circuit    |     |

| D.2  | Experimental results of technology mapping of 0xC4 circuit    |     |

| D.3  | Experimental results of technology mapping of 0xC8 circuit    |     |

| D.4  | Experimental results of technology mapping of 0x0E circuit    | 207 |

xviii

### List of Tables

| 4.1 | Sample parameter values for threshold value and timing analyses. | 42  |

|-----|------------------------------------------------------------------|-----|

| 4.2 | Intermediate propagation delays of genetic logic circuits        | 52  |

| 6.1 | Boolean replacement rules.                                       | 84  |

| 7.1 | Threshold and propagation delay values obtained in D-VASim       |     |

|     | prior to model checking in Uppaal.                               | 104 |

| 7.2 | Threshold and propagation delay values obtained in D-VASim for   |     |

|     | upper and lower bounds of $k_d$ values found in Uppaal           | 108 |

| 7.3 | Default parameter values in iBioSim                              | 109 |

хх

## List of Algorithms

| 4.1 | Threshold value and propagation delay analysis   | 0  |

|-----|--------------------------------------------------|----|

| 5.1 | Main procedure of logic analysis                 | 59 |

| 5.2 | Input-cases analysis                             | 60 |

| 5.3 | Variation analysis                               | 53 |

| 5.4 | Filtration and boolean expression construction 6 | 6  |

| 6.1 | Logic optimization                               | 33 |

| 6.2 | Logic synthesis                                  | 37 |

| 6.3 | Technology mapping                               | )3 |

ххіі

### CHAPTER 1

### Introduction

An advancement in the understanding of cellular processes and DNA synthesis methods suggests that the living cells can be viewed as a *programmable* matter. With this revolutionary finding, logical computations can be performed inside a living cell through a group of biological components, collectively called *genetic circuits*. A genetic circuit represents a gene regulatory network (GRN), which is composed of small genetic components. These components interact with the external signals (like temperature, light, proteins etc.) to control the behavior of a living cell.

Genetic circuits are a key application of *synthetic biology* which is an emerging engineering discipline to program cell behaviors as easy as computers are programmed. Synthetic biology is defined by synthetic biology.org as;

"(a) the design and construction of new biological parts, devices and systems and (b) the re-design of existing natural biological systems for useful purposes".

Biologists are interested in synthetic biology because it provides a viewpoint to analyze, understand, design and ultimately build a biological system. Engineers, on the other hand, are attracted towards synthetic biology because the living world has the abundant mechanisms for controlling life behavior and processing information.

### 1.1 Why computations in cells?

There are numerous complex computations a living cell performs on the continuous environmental signals they encounter. The natural biological systems can be engineered to perform sophisticated computations in living cells. Biologists and engineers are working together on synthetic biology [1] to design new and useful biological systems. The synthetic biological systems performing digital [2] and analog [3] computations have already been implemented.

The artificial computation in living cells will revolutionize the industry of medicine and biotechnology. The aim of performing synthetic computations in living cell is to develop genetic devices to address real-world problems. These problems include the development of genetic systems to detect and destroy cancer cells [4]; production of liquid biofuels to address the global energy and environmental problems [5]; consuming toxic wastes to avoid environmental pollution; and the production of drugs to treat health problems like Malaria [6], to name a few.

### 1.2 State-of-the-art

Similar to *electronic design automation* (EDA) processes which dramatically enhanced the design, verification, validation and production of electronic circuits, researchers have started to work on the development of *genetic design automation* (GDA) tools [7] to automate the design, test, verification and synthesis processes of genetic circuits prior to their validation in laboratory. There are several GDA tools (see Section 2.4) which allow synthetic biologists to design genetic circuits at a high level of abstraction with the focus on a desired function, rather than exact genetic components used to achieve this functionality. By encoding standardized data, genetic circuit construction and analysis has been automated. This not only has reduced the lengthy design process and iterative tests for constructing complex genetic circuits, but has also promoted the reuse of experimentally tested genetic components.

The modern trend to analyze genetic circuits is to perform *in-silico* (in computer) analysis either by solving ordinary differential equations (ODEs) or by performing stochastic simulations, with the aim to reduce the number of required in-vitro (in laboratory) experiments. In order to perform these analyses in a computer, models of biological systems must be represented in a standard computerized format. Several different methods have been proposed to represent and analyze genetic systems [8]. Among these methods, the most widely used standards to represent the *behavior* and the *structure* of a genetic model are the Systems Biology Markup Language (SBML) [9], and the Synthetic Biology Open Language (SBOL) [10], respectively. Unfortunately, no single standard exists which can be used to represent both the behavior and the structure of a biological model. SBML allow users to define the behavior of a circuit by specifying the species of a genetic network and how they interact with each other through chemical kinetics. SBOL, however, is used to illustrate genetic designs graphically with the help of standardized vocabulary of schematic glyphs (SBOL Visual) as well as standardized digital data (SBOL Data). More information on *standards* can be found in Section 2.3.

### 1.3 Motivation

Synthetic biology not only aims to play with natural biological systems but also to construct artificial complex systems from the library of well-characterized biological components, in a similar way as electronic circuits are designed and constructed. While comparison with electronic circuits is useful, there are several important challenges which make the design of genetic circuits more challenging. For instance, genetic components, in contrast to electronic components, are not physically separated from each other. This not only makes the reuse of genetic components in the same system more difficult, but also increases the cross-talk with the neighboring circuit components. Also, the electronic logic gates are composed of transistors which have well-defined and uniform threshold voltage levels that categorizes the logic levels 0 and 1. However, in genetic circuits, each genetic gate is composed of different genetic components which results in the different threshold concentration values. Additionally, in comparison to electronic circuits which have the same physical quantities as input and output signals, the genetic circuits have different species at the input and other at the output, which makes the genetic modules integration more difficult.

As electronic engineers develop circuits using electronic logic gates (such as AND, NAND, and NOT gates), genetic engineers use biological equivalents of these components to control the function of a cell [2, 11]. The field of genetic circuit design is still immature and only small circuits, containing limited number of genes, can be constructed in the laboratory. However, genetic circuits can be designed from a very large number of genetic parts [12] creating a large space of possible solutions even for circuits of limited complexity.

The current practice is to design such circuits directly in the laboratory, through trial and error, which is a time consuming and costly process, as thousands of circuits may have to be tested in order to find a few that works. Due to this, the process of design and implementation of genetic circuits remains very slow. To address these challenges, it is necessary to improve computer aided design (CAD) tools to speed up the design and analyses procedures of genetic circuits. In particular, it is necessary to develop tools which allow genetic design engineers to capture and analyze the stochastic behavior of biological systems dynamically in a way that sounds natural to them.

### 1.4 Present Challenges

An electronic design engineer would never fabricate a circuit on silicon prior to its functional validation and behavioral analysis. Similarly the most important phase in GDA is the simulation and *in-silico* (in computer) analysis of genetic circuit models to increase the chances that the system would work *in-vivo* (in living organism) correctly. There are plenty of tools developed to simulate the behavior of genetic circuits [13]. These tools, however, lack some important and useful features which can not only increase the designer's productivity but also help them design genetic circuit models more effectively. Out of many challenges in the field of GDA, some of the challenges, listed below, have been addressed in this thesis. We believe that addressing the following challenges will not only increase the productivity of genetic design engineer but will also increase the reliability and robustness of genetic circuit models.

### 1.4.1 Virtual experimentation

First, it would be very helpful for biologist or design engineers to have a tool which allow them to perform laboratory experiments virtually in-silico. This corresponds to an experimental environment where a user can trigger the concentrations of input species or change the parameter values (for example, increasing temperature) at any instant of time and observe their live effects on the model's behavior. For in-silico analyses, the standard way to capture the instantaneous, discontinuous state change in the model is by defining *events* (see Section 2.3 for more details). For example, events (shown as green-boxes in Figure 2.6(b)) are used to trigger the concentration of input species to a certain level, at a specific point in time, and to observe the effects on the concentration of output species. A single event can be used to represent only one instance of triggering the concentration to a certain level at a specific time. Since events are predefined, they cannot be changed during runtime, which means that the output of a genetic circuit can be observed only for defined events. In order to observe the output, the different set of input conditions, i.e., when to change

what input to which level, must be defined in each event. Even for moderate sized genetic circuits, capturing all combinations of inputs and concentration levels may require a very large number of events to be defined and simulated. To the best of our knowledge, there exist no tools that allow users to trigger/change input species on the fly during the simulation, effectively creating a *virtual lab*.

### 1.4.2 Timing and threshold analysis

In contrast to EDA tools which allows a user to perform timing analyses, to the extent of our knowledge, no GDA tool allows a user to perform timings and threshold value analyses for genetic gates/circuits. Electronic design engineers do not need to estimate the threshold value for each electronic circuit because these values are well defined and holds valid for all electronic logic gates. However, this is not the case for genetic gates where each of them are composed of different components and have different input and output molecular identities. Therefore each genetic gate may have different input threshold values and thus exhibit different timing behaviors. It is therefore necessary to have such a tool which should assists a user in identifying the correct input threshold concentration required to trigger the circuit's output along with the estimation of propagation delays. It may also help a user to perform in-vitro experimentation quickly by applying the estimated threshold concentration values at input (rather than following *trial-and-error* approach) and expect the circuit's output to be triggered approximately within the time estimated as a propagation delay.

Similar to electronic circuits where timing analysis is a vital design characteristic, the timing analysis may also become an essential design characteristic in genetic circuits. It is therefore very important to have such analyses *in-silico* prior to the circuit's implementation *in-vivo*.

### 1.4.3 Automatic logic validation

It is also interesting to automatically validate if the behaviour of a genetic circuit complies with the design rules. For example, the behavior of a genetic AND gate can be validated by applying all the possible input combinations and determine if the circuit's response obeys the AND Boolean logic. It might be easier to analyze the logical behavior of small circuits by just looking at response curves, but it may become a cumbersome task if the behavior is to be validated manually for complex genetic circuits. Therefore, an automated approach for analyzing the logic in genetic circuits will be helpful.

### 1.4.4 Effortless circuit designing

One of the several challenges in making the design process of genetic gates easier and user-friendly is to let the designers construct genetic circuits at a very high level of abstraction. Recently a tool, named Cello, is developed [14] which allows users to program genetic circuits as easy as electronic circuits are designed through *hardware description language* (HDL). Cello provides user, specially *computer scientist*, a fairly high-level of abstraction to develop genetic circuits without worrying about the underlying physics of genetic interactions. However, this still requires a *biologist* to learn programming principles and the syntax in which the design module should be written. To let the *biologists* design genetic circuits effortlessly without additional prerequisites, a further simple and straightforward mechanism should be developed.

### 1.5 Thesis Contributions

The main aim of this research is to enhance the advancement of GDA tools for analysis, verification, and synthesis of genetic logic circuits. The contributions of this dissertation are the development of the following methods and tools to address the challenges mentioned in Section 1.4:

#### • Virtual laboratory simulation environment (D-VASim)

A simulation tool, named D-VASim (Dynamic Virtual Analyzer and Simulator) is developed, which allows a user to carry out *virtual lab experiments* as an interactive process during runtime, rather than a batch process which is a current practice. It is a user-friendly software with an intuitive graphical user interface, and allows a user to perform both deterministic as well as stochastic simulations. This software tool is available to download freely for public use from http://bda.compute.dtu.dk/downloads/d-vasim/.

• Timing Analyzer (A plugin to D-VASim)

A methodology is introduced to perform the timing and threshold value analysis of genetic logic circuits. This methodology is integrated in D-VASim as a plugin tool.

### • Logic Analyzer (A plugin to D-VASim)

A method is introduced to validate the boolean logic of a genetic circuit from the stochastic simulation data. This boolean logic analysis algorithm is scalable and able to analyse n-input genetic logic circuits through an automated process. This tool is also integrated to D-VASim as a plugin tool.

#### • GeneTech (Standalone tool)

An optimization, synthesis and technology mapping tool for genetic logic circuits. This tool is able to construct a genetic circuit using the library of genetic gates developed at MIT and Boston universities. It is currently a standalone tool but can be integrated to D-VASim as a plugin. GeneTech provides a user an ability to develop genetic circuits only by specifying its behavior in the form of a Boolean expression. With this ability, users, specially biologists, do not need to learn any additional programming language for designing genetic circuits. This tool can be downloaded from http://bda.compute.dtu.dk/downloads/genetech/.

#### • Use of D-VASim with other tools

Besides above mentioned contributions, the research is further extended to demonstrate how D-VASim tool can be used along with existing tools for useful purposes. In particular, the experimental flow for model checking of genetic circuits, using Uppaal [15] and D-VASim [16], has been proposed. Also, an effort has been made to use Cello [14] parameters for simulating the models of real genetic circuits.

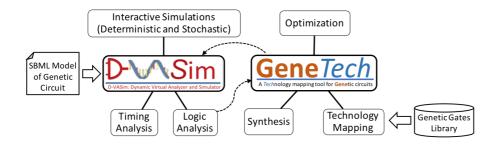

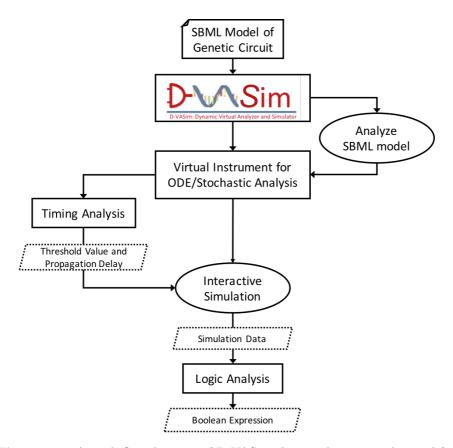

Figure 1.1 shows a very high level diagram which describes how the major contributions made in this dissertation can be used. Having the SBML model of a genetic circuit in D-VASim, users can perform ODE and stochastic simulations in an environment which gives them a feeling of being in the lab performing live experiments by interacting with the model during run-time. Similar to many EDA tools which allow hardware design engineers to perform timing analysis of electronic circuits, D-VASim is the first tool which provides users an ability to perform the timing analysis of genetic circuits. Furthermore, the experimental data, generated from stochastic simulations, can be used to analyze the logical behavior of a genetic circuit. Another tool, *GeneTech*, takes a raw Boolean expression as an input and generates all the possible circuits (in the form of structure) to achieve a desired logic. The dotted line between GeneTech and the D-VASim logic analyzer shows that the Boolean expression generated from the logic analyzer can also be used to obtain other possible circuits for the model being simulated. The circuits are generated using the genetic gates library [14]. The generated models of genetic circuit can then be synthesized into SBML form using any SBML-synthesis tool (like iBioSim [17]) and then can be analyzed back in D-VASim again.

Figure 1.1: The abstract diagram showing how the contributions of this dissertation can be used.

### 1.6 Thesis Organization

This dissertation is organized as follows. **Chapter 2** gives the information about genetic circuits. This chapter gives some basic knowledge of genetic terminologies and a brief overview of how genetic systems work. It describes *standards* in more detail and also give information about existing GDA tools.

**Chapter 3** gives a brief overview of D-VASim. It briefly describes the whole simulation flow with the help of an example circuit model. The details of each subsequent step in this flow is discussed in separate chapters.

In chapter 4, the methodology of timing analysis of genetic logic circuits is presented. This chapter discusses the algorithm developed for analyzing the threshold value and propagation delay of a genetic circuit model. The experimental results are included to support the significance of timing analysis in genetic logic circuits.

**Chapter 5** explains the methodology developed to analyze and verify the logical behavior, of a genetic circuit, from the stochastic simulation data. This chapter also contains the experimental results of logic analysis on different genetic circuit models and the performance evaluation of the algorithm.

The approach for synthesis and technology mapping of genetic circuits is provided in **Chapter 6**. This chapter begins with describing the algorithms developed for reducing the Boolean expression of genetic gates into an optimized form, followed by its synthesis into NOR-NOT form. Then the methodology of technology mapping, along with the discussion of how the genetic gates library is constructed from the data disclosed in [14], is presented. In the end, some experimental results on case study have been presented.

In Chapter 7, it has been demonstrated how D-VASim can be used in collaboration with other tools to perform useful tasks. First an experimental flow is proposed for the statistical model checking of genetic circuits using Uppaal [15] and D-VASim [16]. The experimentation on genetic circuit models are performed to explore their design parameter sensitivity using Uppaal SMC [18]. Next, an attempt is made to show that how Cello [14] parameters can be used to perform simulation.

**Chapter 8** concludes this research work with the discussion of possible future directions.

**Appendix A** contains the supplementary data of Chapter 3, which includes the sample ODE and stochastic simulation results produced by D-VASim.

**Appendix B** contains the supplementary data of Chapter 4. It consists of the timing analysis results for all the genetic circuit models being experimented.

The complete experimental data for the logic analysis (Chapter 5) is enclosed in **Appendix C**.

The extended experimental data related to Gene**Tech** (Chapter 6) is given in **Appendix D**

D-VASim Quick Start Guide (QSG) is included in the Appendix E.

### Chapter 2

## Genetic Circuits

A biological system is composed of living organisms which consists of one or more living cells. The behavior of each of these cells is controlled by genetic circuits which perform dedicated tasks to achieve the overall functionality of a biological system. These genetic circuits, which are composed of several biological components (called the genes network) regulate the amount of proteins in a cell. This gene-regulated network is triggered by external signals, for example, light, temperature, presence of specific proteins, etc., to control the behavior of a living cell, effectively exhibiting a Boolean logic function. The aim of this chapter is to briefly introduce genetic circuits to the audience not familiar with synthetic biology. Section 2.1 gives a brief overview of biology and some basic terminologies, frequently used in genetic design, which are necessary to be known specially to the computer scientists or engineers who do not have primary knowledge of synthetic biology. Next, Section 2.2 presents an example of regulated transcription in lac operon and explains its genetic logic. Section 2.3 gives more information on the standards and Section 2.4 gives a brief overview of GDA tools.

# 2.1 Central Dogma of Molecular Biology

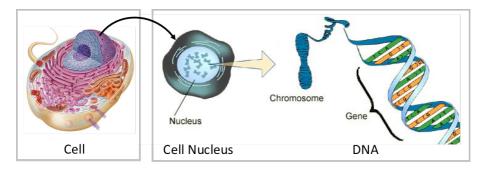

The *Living Cell* is the smallest biological unit of any living organism, and is often called the *building block of life*. Each cell is composed of several organelles like mitochondria, ribosomes, nucleus etc. The *nucleus* is the largest cellular component which contains part or all of the cell's genetic information. This genetic information is stored in the *deoxyribonucleic acid* (DNA) molecule, which is packaged into a thread-like structure called *chromosomes*. DNA is further divided into a group of nucleotide sequences called *genes*. Figure 2.1 shows the relationship between the eukaroytic cell's nucleus, chromosomes in the nucleus, and genes.

Figure 2.1: The hierarchical relationship of living cell and gene. (Image courtesy of BBC Science<sup>1</sup>)

DNA is composed of two nucleotides strands coiled around each other to form a double-helix structure. Each of these strands contain a sequence of four nucleobases - cytosine (C), guanine (G), adenine (A) and thymine (T). These bases on both of the strands bind to each other in pairs such that A only binds with T and G only binds with C. The sequence of these base-pairs codes for various genetic components including, promoters, operators, genes, etc.

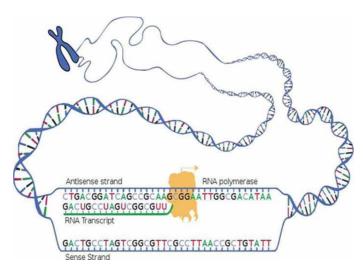

Each gene is a region of DNA which generates a specific protein through the processes called *transcription* followed by *translation*. During transcription, the particular region of DNA (gene) is converted to *ribonucleic acids* (RNAs) by another RNA molecule called *RNA polymerase* (RNAP), which binds to a specific region of that gene called the *promoter*. RNA polymerase then moves along the gene's coding sequence and temporarily breaks the bond between the two DNA strands causing it to unwind or unzip. During this unwinding process, the RNA transcript is generated as shown in Figure 2.2. This process of RNAP

$<sup>\</sup>label{eq:linear} {}^1 \\ \texttt{http://www.bbc.co.uk/schools/gcsebitesize/science/edexcel/classification\_inheritance/genesandinheritancerev1.shtml}$

generation continues until the moving RNAP reaches a region of DNA called *terminator*. At this instant, RNAP leaves DNA and the newly formed RNA is released. Many of these RNAs holds the instructions for constructing protein, and are commonly termed as *messenger RNAs* (mRNAs).

Figure 2.2: The process of transcription. (Image courtesy of the National Human Genome Research Institute)

Now, during the process of translation, another protein, the ribosome, binds to mRNA at its specific region, called the ribosome binding site. The ribosome moves along mRNA and generate the specific proteins. This process of converting DNA into mRNA through transcription and then the conversion of mRNA into protein through translation is known as the central dogma of molecular biology [19].

There are two types of gene expressions, *constitutive* and *regulated*. A Gene is expressed constantly in constitutive type of gene expression, whereas it is controlled and dependent on the environmental changes in regulated gene expression. The genetic circuits are based on the genes which are transcribed through regulation. This transcriptional regulation is carried out by regulatory proteins, called *transcriptional factors*, which binds to an *operator site*, a region of DNA near promoter. The transcription factor either block (referred to as *repressor*) or help (referred to as *activator*) RNAP to bind to the promoter region to initiate a process of transcription.

# 2.2 Example Genetic Circuit: Lac Operon

One of the classical systems used to investigate the transcriptional regulation of *Lac Operon*, was presented by Jacob *et al.* in [20]. *Operon* is referred to as a region of DNA which consists of a group of genes controlled by a single promoter. Lac operon (or lactose operon) is required for the transport and metabolism of lactose in the bacterium *Escherichia coli*, and it was the first gene-regulatory network to be explored clearly.

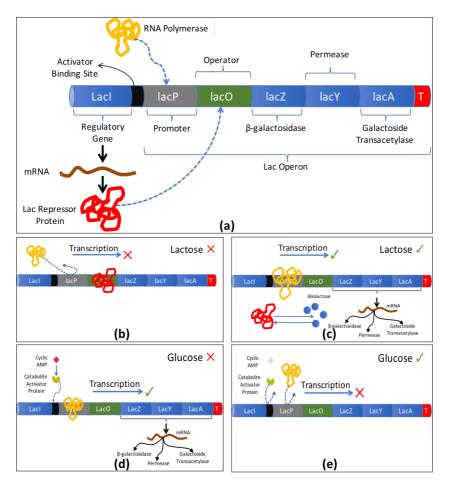

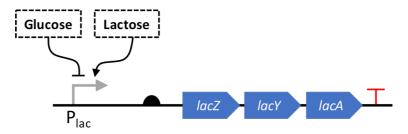

Figure 2.3: Transcriptional regulation of lac operon. (a) Structure of Lac operon. No transcription when (b) lactose is absent and (e) glucose is present. Transcription begins when (c) lactose is present and (d) glucose is absent.

Figure 2.3(a) shows the structure of the lac operon. Three genes, lacZ, lacY, and lacA are required, as a cluster, to utilize lactose by the bacterium. The lacZ, lacY and lacA genes code for the enzymes *beta-galactosidase*, *lactose permease* and *galactoside transacetylase*, respectively. The *lacP* is the promoter region which transcribes the lacZ, lacY and lacA genes as a single *polycistronic* mRNA. The *lacO* region is an operator site to which a transcription factor binds to regulate gene expression. The complete unit consisting of the lac promoter (lacP), lac operator (lacO), and the three genes (lacZ, lacY and lacA) is known as the *lac operon*. The *lacI* is the regulatory gene of lac operon that codes for an mRNA that is translated to produce a protein known as *lac repressor*. The "T" (shown as red region) corresponds to the terminator region where the RNAP stops transcription. The black region between lacI gene and the lac promoter is the *activator binding site* (ABS), which helps RNA polymerase (shown as yellow structure) to bind to the promoter site.

As shown in Figure 2.3(b), when the lactose is not available inside the cell, the lac repressor recognizes the operator site and binds to it tightly. This prohibits the RNA polymerase to recognize the promoter region, and thus prevents the operon to be transcribed. When lactose enters the cell, a small amount of it is converted to *allolactose*, which binds to the lac repressor. This causes a structural change in the lac repressor protein that prevents it from binding to the lac operator site. When lac repressor is not bound to an operator site, RNAP easily binds to a promoter region and transcribe the polycistronic mRNA. This mRNA is then translated to produce beta-galactosidase, lactose permease, and galactoside transacetylase proteins, as shown in Figure 2.3(c).

The discussion of Figure 2.3(b) and (c) indicates that the lac operon is transcribed when lactose is present inside the cell. However, the binding of RNAP, to a promoter site, weakly depends on the presence of lactose, and strongly on the presence of the *catabolite activator protein* (CAP) inside the cell. CAP attaches to an *ABS* and helps RNAP to bind to the promoter region to drive high levels of transcription. The CAP cannot directly bind to an ABS, rather it is regulated by a small molecule known as *cyclic AMP* (cAMP), which acts as a "hunger signal" when the glucose levels inside the cell are low. Therefore, when the glucose level is low, the cAMP bind to CAP and make it able to attach to the ABS. When CAP attaches to the activation binding site, it helps RNAP to bind to the promoter region strongly, and begin transcription. This process is shown in Figure 2.3(d).

On the contrary, when the glucose level rises, it reduces the concentration of cAMP, which in turn makes the CAP unable to attach to the ABS. Without CAP being attached to the ABS, RNAP cannot attach to the promoter region and thus the transcription process is stopped, as shown in Figure 2.3(e).

#### 2.2.1 Genetic logic in lac operon

From the discussion above, the natural genetic logic exist in the transcriptional behavior of lac operon can be extracted. Figure 2.4(a) summarizes the logical behavior of lac operon in the form of truth table, with inputs being *Glucose* (G) and *Lactose* (L), and the output being *Transcription* (T) of lacZ, lacY and lacA genes.

| Inp | uts | Output |           |

|-----|-----|--------|-----------|

| G   | L   | Т      |           |

| 0   | 0   | 0      | · ·→∽→ ∖, |

| 0   | 1   | 1      |           |

| 1   | 0   | 0      |           |

| 1   | 1   | 0      |           |

|     | (a) |        | (b)       |

Figure 2.4: Genetic logic in lac operon. (a) Truth Table. (b) Circuit schematic.

When glucose is absent (logic 0), CAP binds to ABS and RNAP should perform transcription. However, when the lactose is also absent (logic 0), the *lacI repressor* protein binds to the operator region and blocks RNAP to move along the DNA strand to perform transcription. Therefore, transcription is always blocked whenever lactose is absent in the cell. Similarly, when glucose is present in the cell, it prohibits CAP to bind to ABS and thus reduce the affinity of RNAP to bind to the promoter region to begin transcription. However, when glucose is absent and lactose is present, the lac operon is transcribed, resulting in the Boolean logic shown as a circuit diagram in Figure 2.4(b).

#### 2.2.2 The standard SBOL representation of lac operon

Figure 2.4(b) gives a fairly low-level details of how lac operon works, which is not the standard way of representing any genetic system. As mentioned earlier in *Chapter 1 - Introduction*, the *SBOL* is the standard way to represent the highlevel diagrams of genetic systems. The equivalent SBOL visual (or SBOLv) diagram of the genetic system for lac operon would be something similar to the diagram shown in Figure 2.5. This figure indicates that a single promoter,  $P_{lac}$ , is responsible for the transcription of three genes, lacZ, lacY and lacA. The presence of glucose represses and the presence of lactose activates the promoter, reflecting that a transcription is initiated when glucose is absent and lactose is present in the cell. The symbol "T" represents the terminator region of DNA where the transcription is stopped. As a result of transcription, an mRNA is produced and the *ribosomes* binds to this mRNA at the *ribosome binding site* (shown as semi-sphere in Figure 2.5), to carry out the production of output proteins *beta-galactosidase, permease* and *galactoside transacetylase*, from the genes lacZ, lacY and lacA, respectively.

Figure 2.5: SBOL visual representation (or SBOLv) of lac operon genetic system.

The example discussed above is a natural genetic logic circuit which exists in the lac operon. Some researchers have already started to engineer custom genetic logic components to achieve a desired logical behavior in a living cell [14, 21]. We have used the SBML models of these genetic logic circuits [14, 21] to test the tools and method presented in this thesis.

### 2.3 Standards

It is mentioned in *Chapter 1 - Introduction* that SBML and SBOL are two major standards to represent genetic model's behavior and structure respectively. Both of these standards are developed by the members of systems and synthetic biology community.

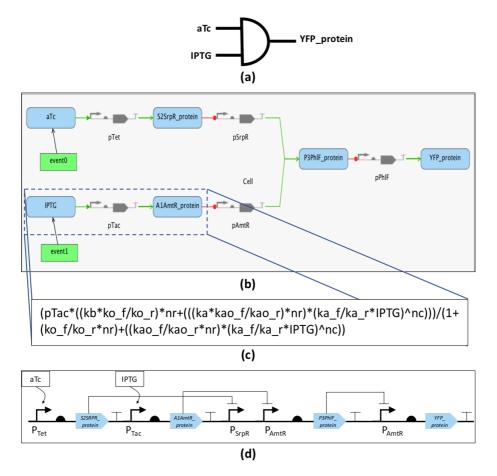

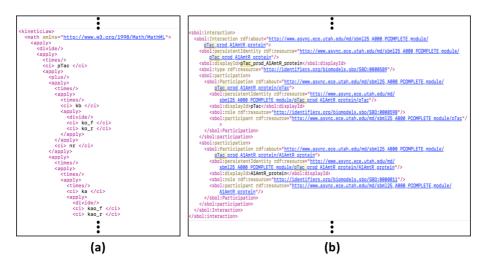

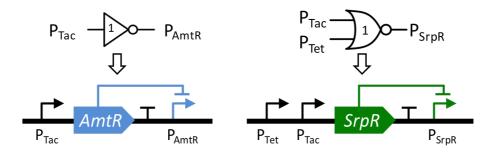

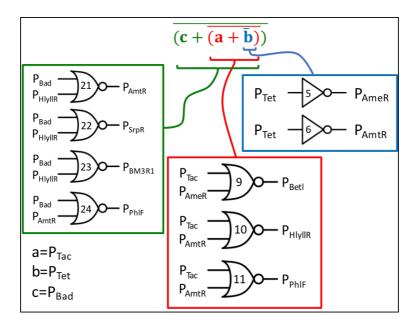

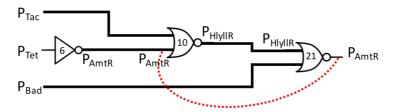

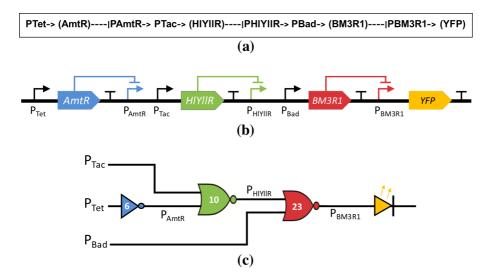

The purpose of SBML standard is to exchange essential aspects of biological model among different softwares and is supported by over 290 GDA tools. It is a machine-readable *eXtensible Markup Language* (XML) that is independent of any specific software language. For example, the SBML model of a genetic AND gate circuit, designed in iBioSim [17], is shown in Figure 2.6(b). Tools which support SBML-synthesis allow users to define the model parameters, species and their biochemical interactions using mathematical expressions. As an example,

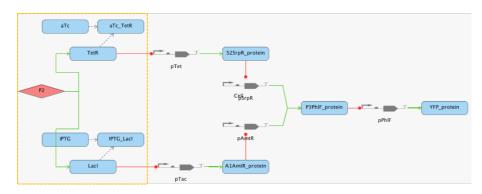

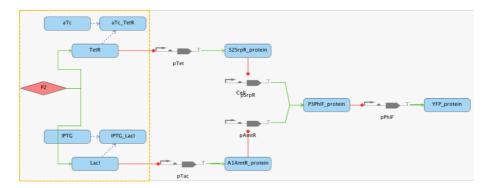

the SBML model of a genetic AND gate circuit is shown in Figure 2.6(b) in which the reaction for pTac, along with an external influence of IPTG inducer, to produce  $A1AmtR\_protein$  is shown in Figure 2.6(c). The values of the parameters in this figure, for example kb,  $ko\_r$ , nc, etc, are defined separately. The different SBML-synthesis tools may have their own icons to represent standard biological processes like *repression*, *activation* etc. For example, in Figure 2.6(b),  $A1AmtR\_protein$  repressing the following promoter pAmtR is shown with the red line having round-headed circle. The same processes are represented differently in different tools.

Figure 2.6: SBML and SBOLv diagram of genetic AND gate. (a) Circuit schematic. (b) SBML model design in iBioSim [17]. (c) Example kinetic reaction. (d) SBOLv diagram.

In order to keep the uniformity in representing these models, the SBOL is developed to document all biological models in a standardized manner. It is an emerging data standard for synthetic biology with growing support among several GDA software tools, including biochemical modeling tools [22–24], design composition tools [22,23,25–27], and sequence editing tools [28,29]. It is also an *eXtensible* standard so it can easily adapt the evolving needs of the synthetic biology community. Figure 2.6(d) shows the SBOLv diagram of the genetic AND gate model shown in Figure 2.6(b).

As said before that different tools may have their own icons to represent the biological processes and species, but all of them are supposed to generate the same XML document in order to be used by other software tools. Figure 2.7(a) and (b) shows the cropped images of SBML and SBOL xml files, respectively, of the same genetic AND gate model shown in Figure 2.6. Both of the images shown in this figure depicts some portion of these SBML and SBOL xml files, showing how the reaction (between pTac and  $A1AmtR\_protein$ ) shown in Figure 2.6(c) are represented.

Figure 2.7: Cropped images of SBML and SBOL files of genetic AND gate circuit shown in Figure 2.6. (a) SBML file. (b) SBOL file.

## 2.4 Genetic Design Automation (GDA) Tools

Numerous computational tools [13,23,30,31] have been developed to assist users in designing genetic circuits through an automated processes. These tools in-

cludes DNA sequence editing, biochemical modeling, design composition, and technology mapping tools. According to [13], there are more than 290 tools which support SBML model construction and simulation; and about 30 of them are GDA tools which support sequence editing, design composition, optimization and technology mapping. Some of these tools serve as a toolbox for commercial platforms including MATLAB, Mathematica, and Oracle; some are developed as APIs or plugins to specific software systems, while others are independent tools for design and simulation.

#### 2.4.1 Sequence editing tools

Sequence editing tools are typically considered low-level tools which enable user to construct, edit or annotate the base-pair sequences of genetic components. These tools include SBOLDesigner [32], Synthetic GeneDesigner [28], GeneDesign [33], VectorEditor [29], and Kera [34]. Only few of the sequence editing tools support the SBOL standard. However, nearly all of these tools support reading and writing plain text DNA sequences that comply with the *International Union of Pure and Applied Chemistry* (IUPAC) codes for *nucleotides* [35] and *amino acids*.

#### 2.4.2 Biochemical modeling and design composition tools

These tools allow users to develop mathematical models and usually also provide users with the ability to analyze these models. They require users to manually compose designs and generate standard files automatically. Some of these tools are CellDesigner [36], BioUML [37], iBioSim [17], COPASI [38], D-VASim [16, 39], Uppaal [15], Asmparts [40], GEC [41], GenoCAD [26], Kera [34], ProMoT [42], Antimony [43], Proto [23], SynBioSS [44], TinkerCell [22], and Cello [14]. Few of these tools also support model checking of genetic circuits including [15, 17, 18, 45, 46].

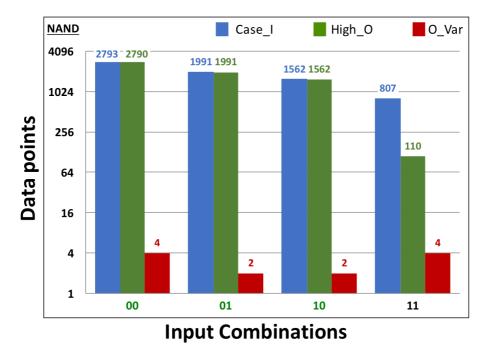

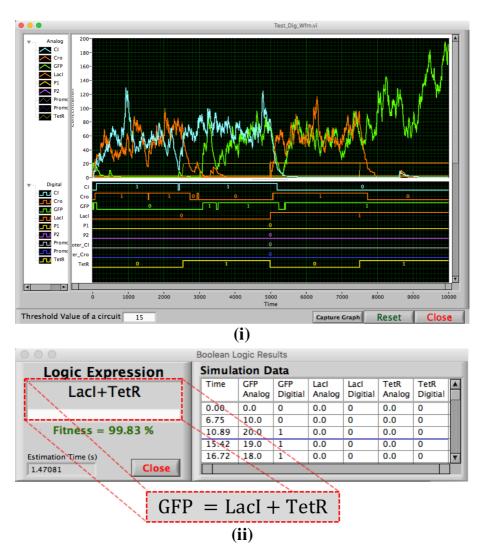

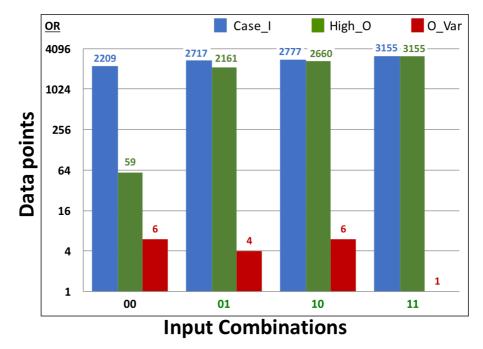

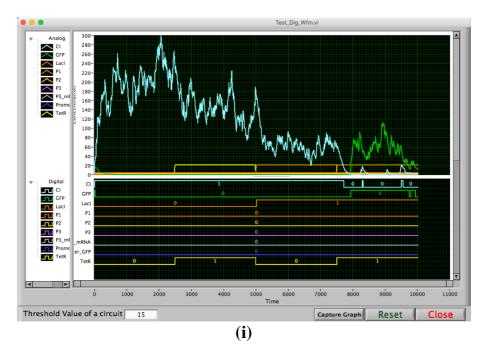

A vast majority of these tools provides different level of support of reading and/or writing SBML files to capture the mathematical behaviour of biological models. For example, CellDesigner, iBioSim, COPASI, and ProMoT support both import and export of SBML files; Asmparts, GenoCAD, GEC and Syn-BioSS, on the other hand, are only able to export SBML; while D-VASim, being a simulation tool, is able to import SBML files only. Each of these tools have their own advantages. For example, iBioSim, Antimony and BioUML tools support hierarchical model composition in a standardized SBML format. iBioSim also supports designing and modifying the DNA sequences of genetic constructs using SBOL data model [32]. Most of these tools support both deterministic and stochastic simulations, including iBioSim, COPASI and D-VASim. A noticeable feature of SynBioSS is that it supports running the complex models on a *supercomputer* to speedup the process of finding genetic parts to construct a desired biological system. An apparent feature of TinkerCell tool is that it provides a platform to integrate third-party algorithms for testing different methods relevant to synthetic biology. The distinctive feature of D-VASim is its virtual simulation environment to let the users perform experimentation by dynamically interacting with the biological models. It also supports *automated* timing and logic analysis of genetic circuits in its virtual simulation platform.